## A CONFIGURABLE H.265-COMPATIBLE MOTION ESTIMATION ACCELERATOR ARCHITECTURE SUITABLE FOR REALTIME 4K VIDEO ENCODING

By

MICHAEL BRALY B.S. (Harvey Mudd College) May, 2009

#### THESIS

Submitted in partial satisfaction of the requirements for the degree of

MASTER OF SCIENCE

in

Electrical and Computer Engineering

in the

### OFFICE OF GRADUATE STUDIES

of the

#### UNIVERSITY OF CALIFORNIA

DAVIS

Approved:

Chair, Dr. Bevan M. Baas

Member, Dr. Rajeevan Amirtharajah

Member, Dr. Soheil Ghiasi

Committee in charge 2015

© Copyright by Michael Braly 2015 All Rights Reserved

## Abstract

The design for a second generation motion estimation accelerator is presented and demonstrated as suitable for H.265/HEVC (MEACC2). Motion estimation is the most computationally intensive task in video encoding, and its share of the processing load for video coding has continued to increase with the release of new video formats and coding standards, such as Digital 4K and H.265/HEVC. MEACC2 has two 4 KB frame memories necessary to hold the ACT and REF frames, designed using a Standard Cell Memory technique, with line-based pixel write, and block-based pixel accesses. It computes 16 pixel sum absolute differences (SADs) per cycle, in a 4x4 block, pipelined to take advantage of the high throughput block pixel memories. MEACC2 also continues to support configurable search patterns and threshold-based early termination. MEACC2 is independently clocked, can sustain a 812 MHz operating frequency and occupies approximately  $1.041 \text{ mm}^2$  post place and route in a 65 nm CMOS technology node. Taken together, MEACC2 can sustain a throughput of 105 MPixels/s while encoding the video stream johnny\_60 with a hexagonal 'ABA' pattern with no early termination, as its worst performance, which is sufficient to encode 720p video at 110 frames per second (FPS). Multiple search algorithms are run against a battery of 6 video sequences using MEACC2. These runs demonstrate the adaptability and suitability of MEACC2 for video coding in H.265/HEVC at high throughput, and also demonstrate the efficacy and tradeoff present in a novel search pattern algorithm, 12-pt Circular Search.

## Acknowledgments

I would like to thank my adviser, Professor Bevan Baas. In 2009, he was willing to take a chance on me, when it seemed like no one else would. His advice, teaching, and example, have helped me build something I am proud of, and the lessons I have learned at UC Davis have continued to help me in my life in industry. I would also thank my parents, who have supported me always, and have allowed me to forge my own path in life, one that I don't think any of us would have imagined when I was still growing up, out in East Davis. Thank you to Trevin, Aaron, John, Brent, and Eman. You guys are awesome, and were always willing to chat about research, even though I was the only one doing any sort of video processing at all! An additional thank you to Aaron, for taking the time to do the final synthesis and place and route flows, and then going above and beyond to play with the density settings to find the optimal P&R result. Finally, thank you Lizzie. For being so very patient.

# Contents

| A             | bstra                                    | $\operatorname{ct}$                                                                                                                                                                                                                                                                                                                                                                              | ii                                         |

|---------------|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|

| A             | cknov                                    | wledgments                                                                                                                                                                                                                                                                                                                                                                                       | iii                                        |

| $\mathbf{Li}$ | st of                                    | Figures                                                                                                                                                                                                                                                                                                                                                                                          | vii                                        |

| $\mathbf{Li}$ | st of                                    | Tables                                                                                                                                                                                                                                                                                                                                                                                           | ix                                         |

| 1             | <b>Intr</b><br>1.1<br>1.2<br>1.3         | oduction         Project Goals         Contributions         Overview                                                                                                                                                                                                                                                                                                                            | 1<br>2<br>2<br>3                           |

| <b>2</b>      | Digi                                     | ital Video Compression                                                                                                                                                                                                                                                                                                                                                                           | <b>4</b>                                   |

|               | <ul><li>2.1</li><li>2.2</li></ul>        | Video Coding Terms in Historical Context from H.261 to H.265         2.1.1       H.261         2.1.2       H.262         2.1.3       H.264         2.1.4       H.265         H.265       Image: Context from H.261 to H.265         1.3       H.265         2.1.4       H.265         H.264 and H.265 in Depth         2.2.1       Macroblocks and Coding Units         2.2.2       Coding Trees | $5 \\ 5 \\ 8 \\ 9 \\ 10 \\ 13 \\ 14 \\ 14$ |

|               | 2.3<br>2.4<br>2.5                        | 2.2.3       Slices and Tiles                                                                                                                                                                                                                                                                                                                                                                     | 16<br>16<br>16<br>17<br>19<br>23           |

| 3             | 3.1                                      | AsAP Platform<br>Generalized Interface                                                                                                                                                                                                                                                                                                                                                           | <b>25</b><br>25                            |

|               | 3.2                                      | Scalable Mesh                                                                                                                                                                                                                                                                                                                                                                                    | 27<br>27                                   |

|               | $\begin{array}{c} 3.3\\ 3.4 \end{array}$ | On-Chip External Memory                                                                                                                                                                                                                                                                                                                                                                          | $\frac{28}{28}$                            |

| <b>4</b> | $\mathbf{Rel}$ | ated Work 29                                                                                                                                                |

|----------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | 4.1            | Early Termination                                                                                                                                           |

|          | 4.2            | Search Patterns                                                                                                                                             |

|          | 4.3            | Frame Memory                                                                                                                                                |

|          |                | 4.3.1 Standard Cell Memories                                                                                                                                |

|          |                | 4.3.2 Reference Frame Compression                                                                                                                           |

|          | 4.4            | Accelerating Motion Estimation                                                                                                                              |

|          |                | 4.4.1 Software Baseline Encoder                                                                                                                             |

|          |                | 4.4.2 Dedicated SAD Instructions for CPUs, Embedded Compute Acceler-                                                                                        |

|          |                | ators                                                                                                                                                       |

|          |                | 4.4.3 GPU-Based Implementations                                                                                                                             |

|          |                | 4.4.4 ASIC Designs                                                                                                                                          |

|          | 4.5            | Comparative Performance                                                                                                                                     |

| <b>5</b> | ME             | 2 Architecture 44                                                                                                                                           |

|          | 5.1            | Instruction Set                                                                                                                                             |

|          |                | 5.1.1 Register Input Instructions                                                                                                                           |

|          |                | 5.1.2 Pixel Input Instructions                                                                                                                              |

|          |                | 5.1.3 Pattern Memory Input Instructions                                                                                                                     |

|          |                | 5.1.4 Output Instructions                                                                                                                                   |

|          |                | 5.1.5 Operation Instructions                                                                                                                                |

|          |                | 5.1.6 Limitations $\ldots \ldots \ldots$    |

|          |                | 5.1.7 Example Programs and Latency                                                                                                                          |

|          | 5.2            | Compute Datapath                                                                                                                                            |

|          |                | 5.2.1 Adder Architecture $\ldots \ldots 69$ |

|          | 5.3            | Pixel Memory         70                                                                                                                                     |

|          |                | 5.3.1 Line Access and Block Access Memory Architectures 70                                                                                                  |

|          |                | 5.3.2 SCMs and Block Access Memory Architectures                                                                                                            |

|          |                | 5.3.3 REF Memory Access Patterns                                                                                                                            |

|          |                | 5.3.4 A Smart Full Search Pattern leveraging Pixel Frame Locality 79                                                                                        |

|          | 5.4            | Pattern Memory 81                                                                                                                                           |

|          |                | 5.4.1 ROM Pattern                                                                                                                                           |

|          |                | 5.4.2 A 12 Point Circular Search Pattern                                                                                                                    |

|          | 5.5            | Control Units                                                                                                                                               |

|          | 5.6            | Output Block    92                                                                                                                                          |

| 6        | ME             | 2 Physical Data 94                                                                                                                                          |

| 7        | Ma             | tlab Model 96                                                                                                                                               |

|          | 7.1            | Model                                                                                                                                                       |

|          | 7.2            | Implementation as a Class                                                                                                                                   |

|          | 7.3            | Automatic Test Generation and Transcription                                                                                                                 |

|          | 7.4            | Cost Functions                                                                                                                                              |

| 8        | Sim            | ulation Results 101                                                                                                                                         |

| 0        | 8.1            | Cost Function Correlation                                                                                                                                   |

|          | 0.1            | 8.1.1 FIFO Limits                                                                                                                                           |

|          |                |                                                                                                                                                             |

|             | 8.2                                                  | Patter                                                                                       | n Search Performance                                  | 103                                           |

|-------------|------------------------------------------------------|----------------------------------------------------------------------------------------------|-------------------------------------------------------|-----------------------------------------------|

|             | 8.3                                                  | Perform                                                                                      | mance Prediction                                      | 107                                           |

|             |                                                      | 8.3.1                                                                                        | From Cost Function to Performance Prediction          | 107                                           |

|             |                                                      | 8.3.2                                                                                        | Performance Prediction Across Video Streams           | 108                                           |

|             |                                                      | 8.3.3                                                                                        | Performance Scalability                               | 108                                           |

| 9           | Cor                                                  | nclusior                                                                                     | 18                                                    | 110                                           |

|             | 9.1                                                  | Contri                                                                                       | butions                                               | 110                                           |

|             | 9.2                                                  | Non-V                                                                                        | ideo Compression Applications                         | 110                                           |

|             |                                                      | 9.2.1                                                                                        | Pattern Matching                                      | 110                                           |

|             |                                                      | 9.2.2                                                                                        | Motion Stabilization                                  | 111                                           |

|             |                                                      | 9.2.3                                                                                        | Burst Memory                                          | 111                                           |

|             | 9.3                                                  | Future                                                                                       | Research                                              | 111                                           |

| 1(          | ) Glo                                                | ssary                                                                                        |                                                       | 113                                           |

|             |                                                      | v                                                                                            |                                                       |                                               |

|             | Ma                                                   | v                                                                                            | odel Code                                             | 118                                           |

|             |                                                      | tlab M                                                                                       | odel Code                                             | <b>118</b><br>118                             |

|             | A.1                                                  | tlab Mo<br>motion                                                                            | n_estimation_engine.m                                 |                                               |

| A           | A.1                                                  | tlab Me<br>motion<br>tlab Ins                                                                | n_estimation_engine.m                                 | 118                                           |

| A           | A.1<br>Mat                                           | tlab Mo<br>motion<br>tlab Ins<br>genera                                                      | struction Generation Code                             | 118<br>141                                    |

| A           | A.1<br>Mat<br>B.1                                    | tlab Me<br>motion<br>tlab Ins<br>genera<br>test_inj                                          | struction Generation Code<br>te_test_from_model_run.m | 118<br>141<br>141                             |

| A           | A.1<br>Mat<br>B.1<br>B.2<br>B.3                      | tlab Me<br>motion<br>tlab Ins<br>genera<br>test_inj                                          | struction Generation Code<br>te_test_from_model_run.m | 118<br><b>141</b><br>141<br>145               |

| A<br>B      | A.1<br>Mat<br>B.1<br>B.2<br>B.3<br>Tes               | tlab Me<br>motion<br>tlab Ins<br>genera<br>test_inj<br>test_ou<br>tbench                     | struction Generation Code<br>te_test_from_model_run.m | 118<br>141<br>141<br>145<br>153               |

| A<br>B      | A.1<br>Mat<br>B.1<br>B.2<br>B.3<br><b>Tes</b><br>C.1 | tlab Me<br>motion<br>tlab Ins<br>genera<br>test_inj<br>test_ou<br>tbench<br>me2_to           | struction Generation Code<br>te_test_from_model_run.m | 118<br>141<br>141<br>145<br>153<br>156        |

| A<br>B<br>C | A.1<br>Mat<br>B.1<br>B.2<br>B.3<br>Tes<br>C.1<br>Top | tlab Me<br>motion<br>tlab Ins<br>genera<br>test_inj<br>test_ou<br>tbench<br>me2_tc<br>-Level | a_estimation_engine.m                                 | 118<br>141<br>141<br>145<br>153<br>156<br>156 |

# List of Figures

| 2.1  | Inter-frame redundancies                                                     |

|------|------------------------------------------------------------------------------|

| 2.2  | Intra-frame redundancies                                                     |

| 2.3  | Example SAD computation                                                      |

| 2.4  | Shapes supported in H.265 and H.264. each square represents a 4x4 block of   |

|      | pixels. Blue shapes are only supported in H.265                              |

| 2.5  | Shapes supported in H.265 including AVMP. each square represents a 4x4       |

|      | block of pixels. Red shapes are AMVP shapes and are not supported by         |

|      | MEACC2 15                                                                    |

| 2.6  | Different kinds of Full Search patterns                                      |

| 2.7  | Example 3-stage pattern search                                               |

| 2.8  | Relationship between search pattern points and pixel blocks                  |

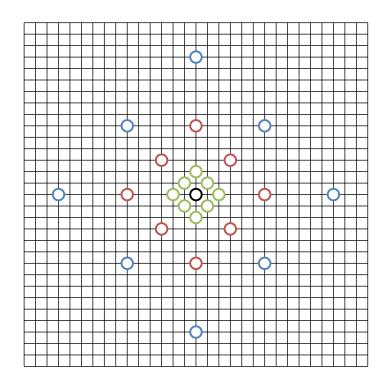

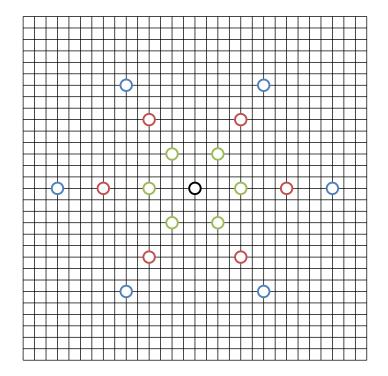

| 2.9  | Cross patterns of varying width                                              |

| 2.10 | Diamond patterns of varying width                                            |

| 9.1  | An MxN AsAP array                                                            |

| 3.1  | e e e e e e e e e e e e e e e e e e e                                        |

| 3.2  | A 167 core AsAP Array with big memories and accelerators                     |

| 4.1  | HexA                                                                         |

| 4.2  | HexB                                                                         |

| 4.3  | HexABA                                                                       |

| 4.4  | HexBAB                                                                       |

|      |                                                                              |

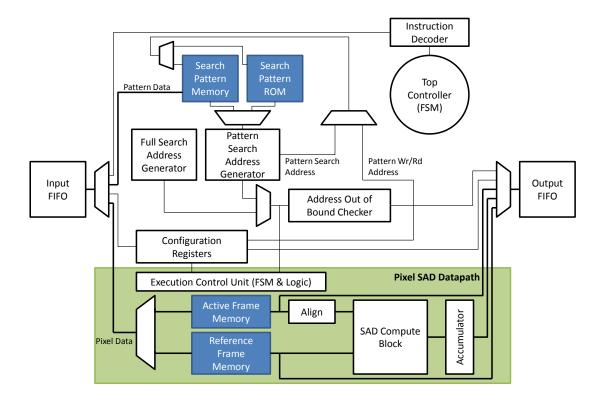

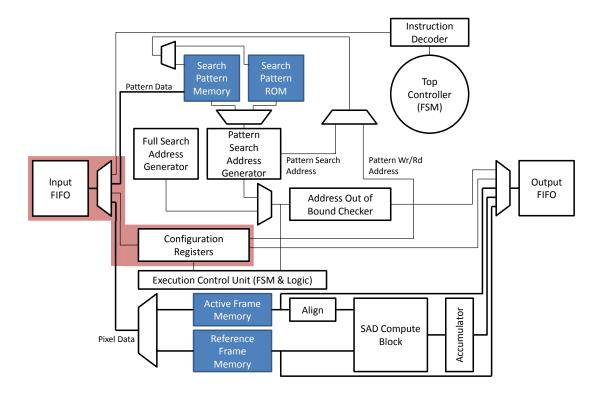

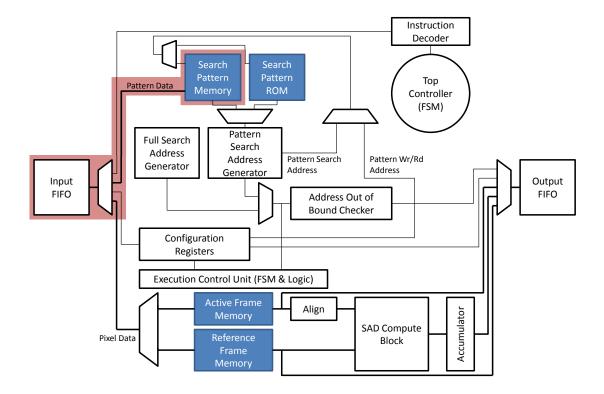

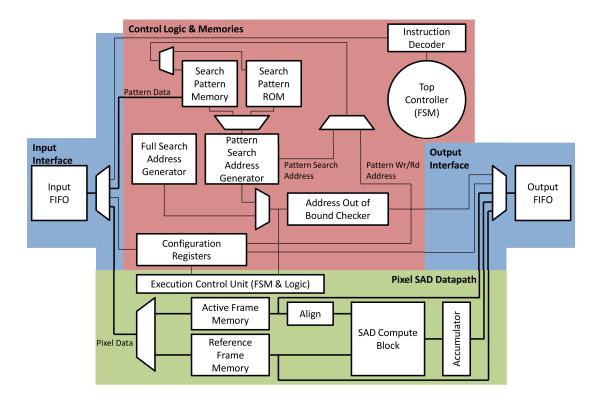

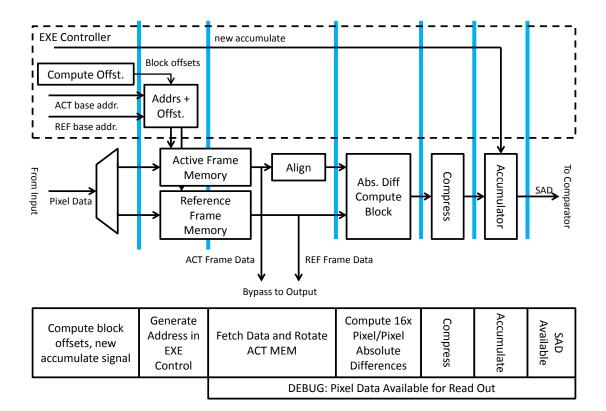

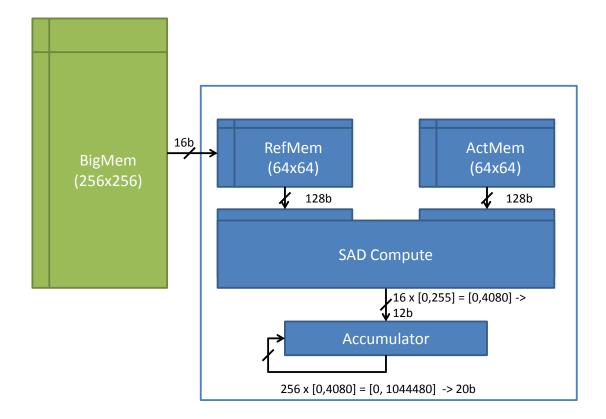

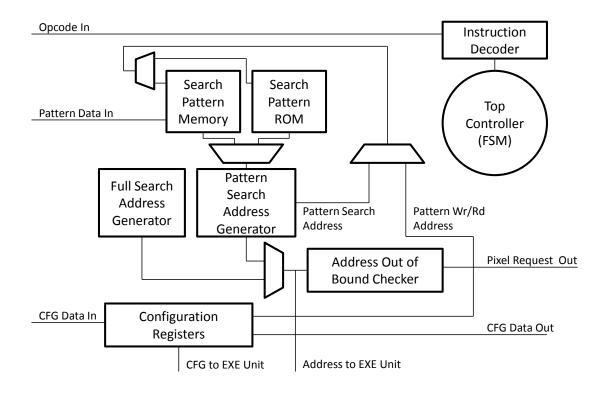

| 5.1  | Top level block diagram    46                                                |

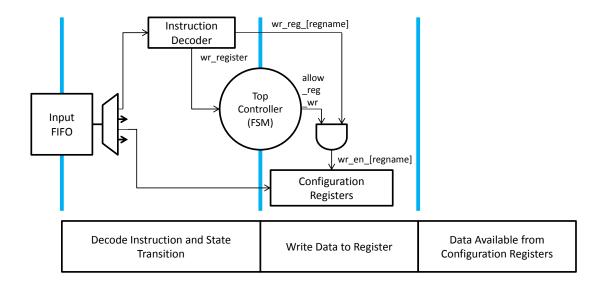

| 5.2  | Top level register input path 47                                             |

| 5.3  | Pipeline diagram for register input instructions                             |

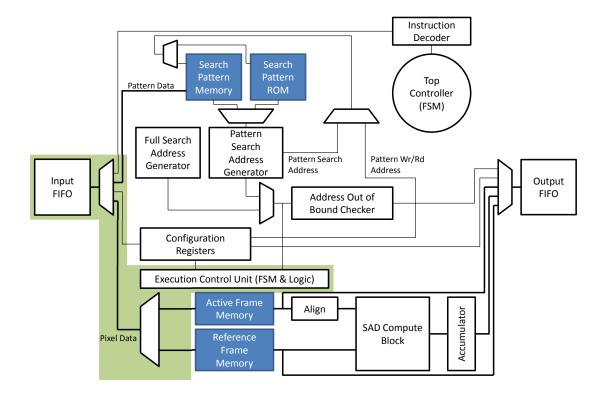

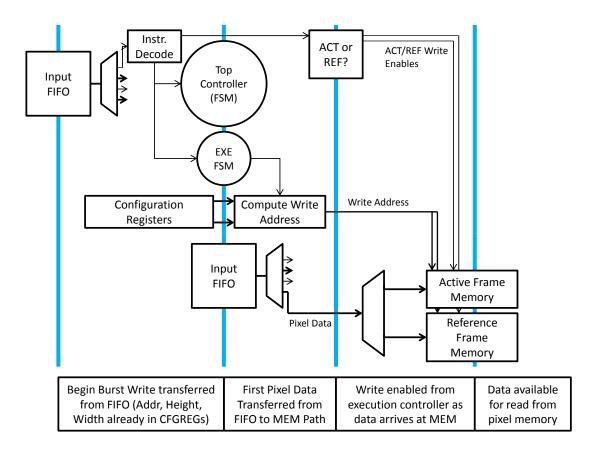

| 5.4  | Top level pixel input path                                                   |

| 5.5  | Pipeline diagram for pixel input instructions                                |

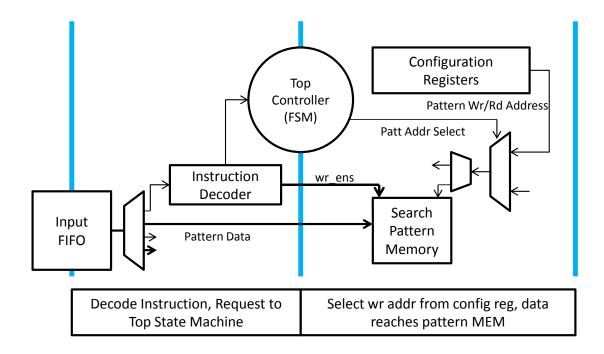

| 5.6  | Top level pattern memory input path                                          |

| 5.7  | Pipeline diagram for pattern memory input instructions                       |

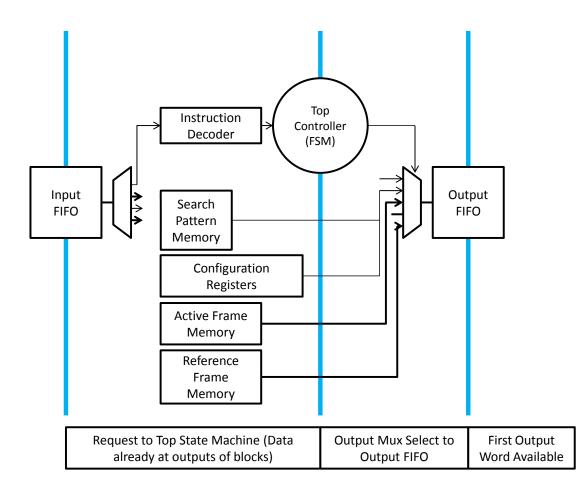

| 5.8  | Top level output path 59                                                     |

| 5.9  | Pipeline diagram for output instructions                                     |

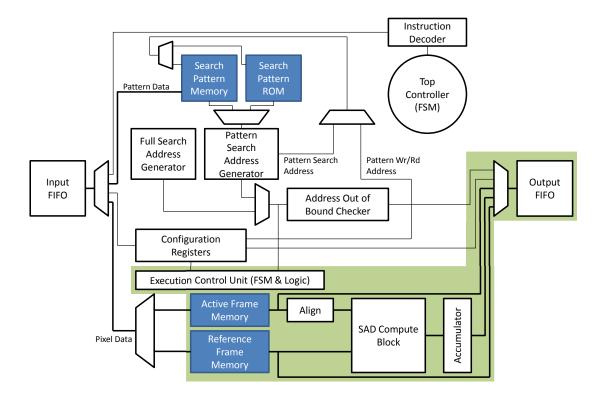

| 5.10 | Top level block diagram annotated by function                                |

| 5.11 | I i i i i i I i i i I i i i i i i i i i                                      |

|      | Required bit widths for full precision throughout the SAD compute process 71 |

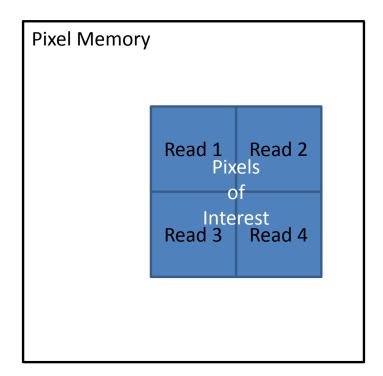

|      | Line based memory access                                                     |

| 5.14 | Block based memory access                                                    |

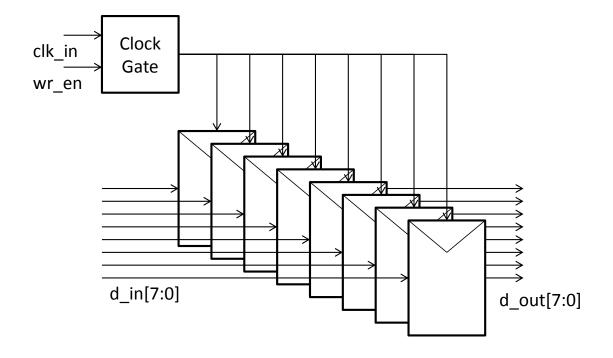

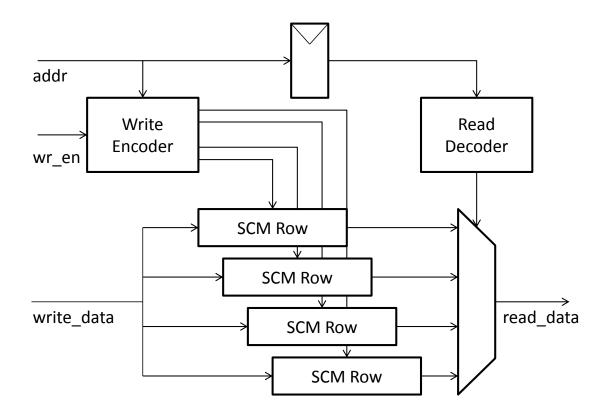

| 5.15 | A word of standard sell memory                           | 74  |

|------|----------------------------------------------------------|-----|

| 5.16 | A multi-word standard cell memory                        | 74  |

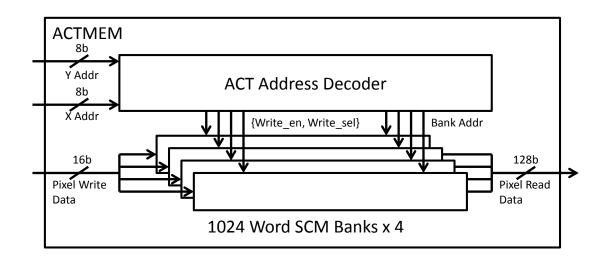

| 5.17 | ACT memory access pattern                                | 75  |

| 5.18 | Component blocks of the ACT frame memory                 | 76  |

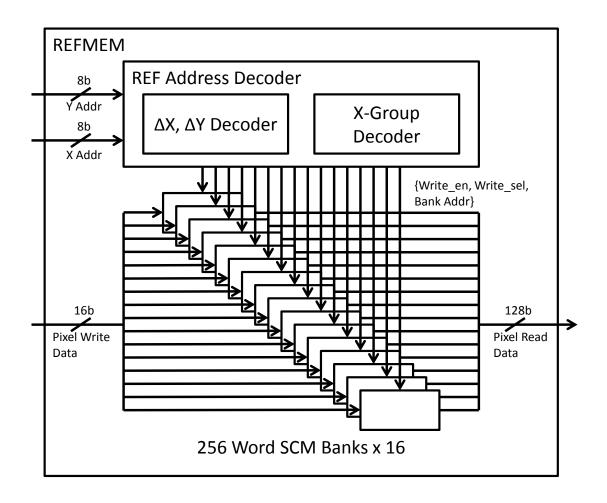

|      | REF memory access pattern                                | 76  |

| 5.20 | Component blocks of the REF frame memory                 | 77  |

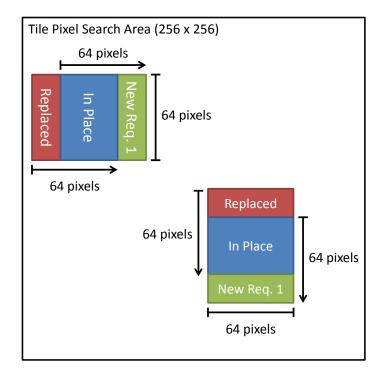

| 5.21 | Memory replacement scheme for cardinal frame shifts      | 79  |

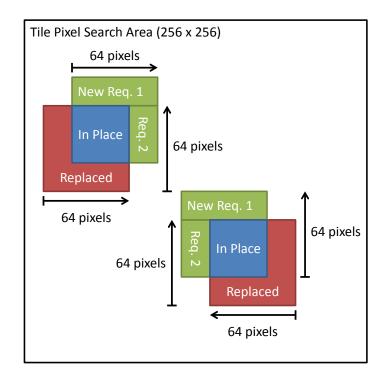

| 5.22 | Memory replacement scheme for diagonal frame shifts      | 80  |

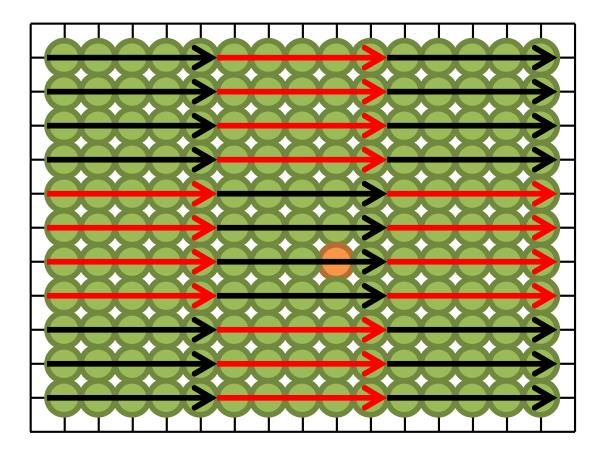

| 5.23 | The pixel checking pattern of a sector based full search | 81  |

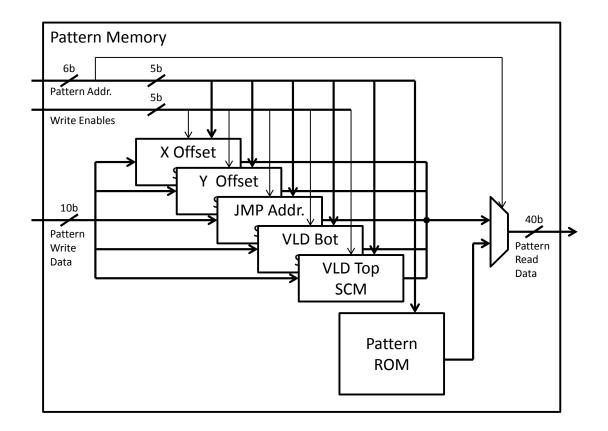

| 5.24 | Component Blocks of the pattern memory                   | 83  |

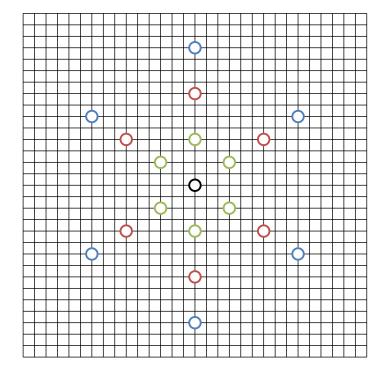

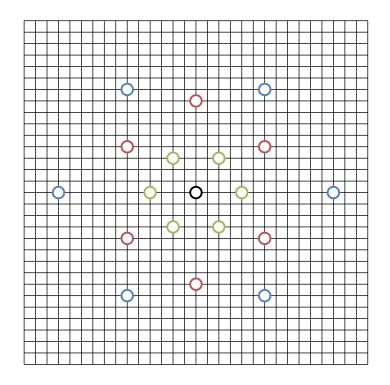

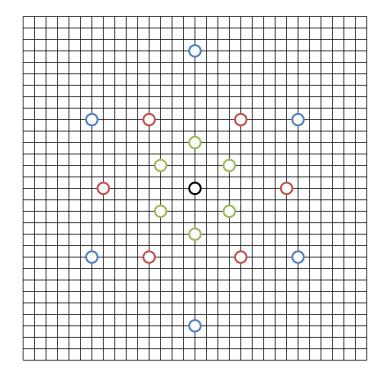

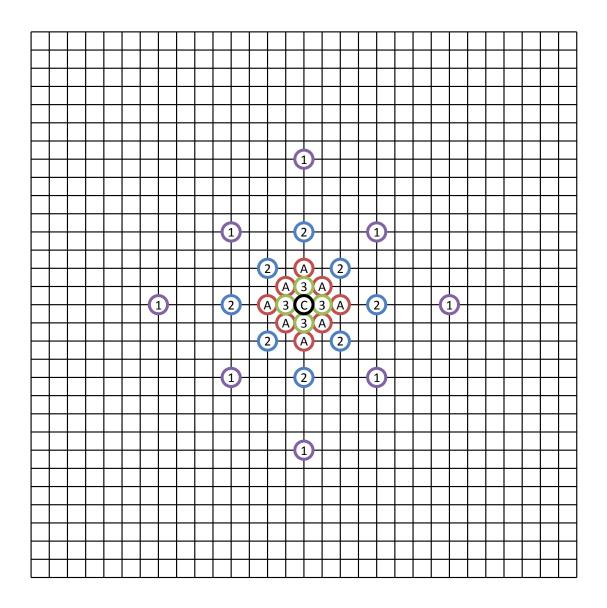

| 5.25 | 4-Stage pattern stored in ROM                            | 86  |

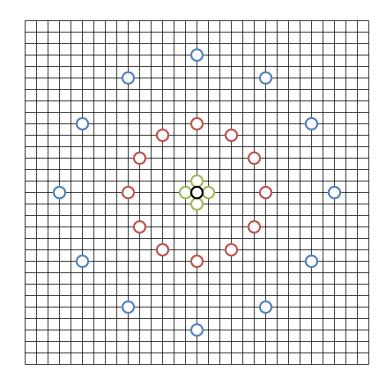

| 5.26 | 3-Stage, 12-point circular pattern                       | 88  |

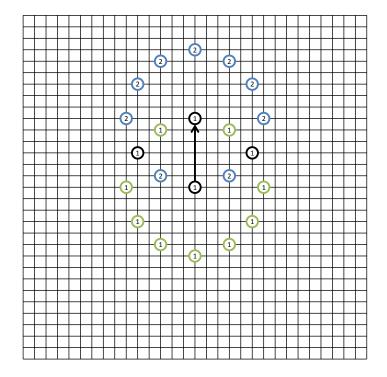

| 5.27 | Circular pattern type I reuse                            | 89  |

| 5.28 | Circular pattern type II reuse                           | 89  |

| 5.29 | Circular pattern type III reuse                          | 90  |

| 5.30 | Controller circuitry                                     | 90  |

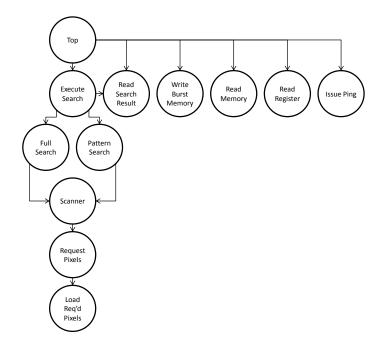

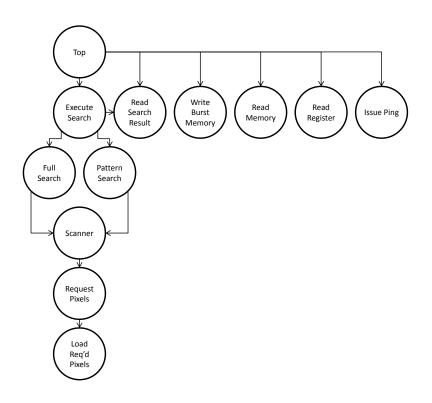

| 5.31 | Hierarchy of the top control unit                        | 91  |

| 5.32 | State diagram of the top level controller                | 92  |

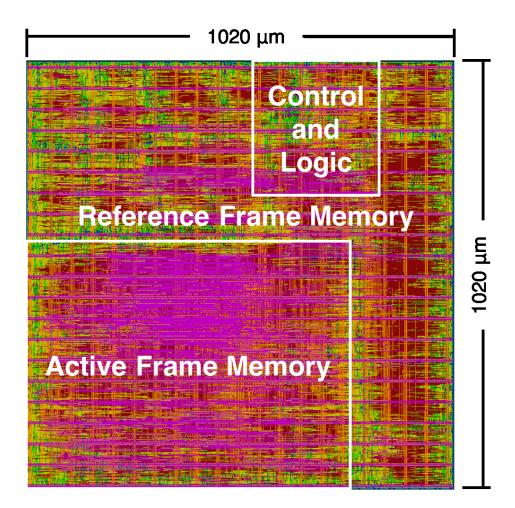

| 6.1  | A plot of the physical layout of the MEACC2              | 95  |

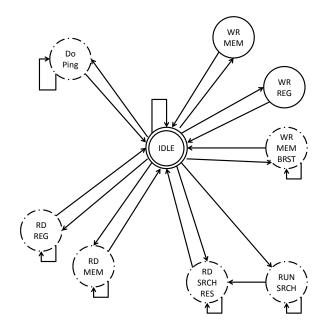

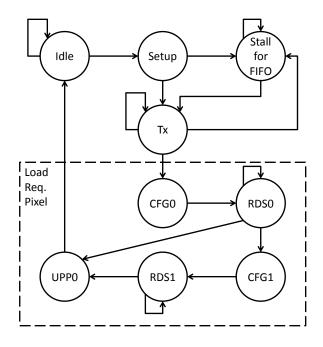

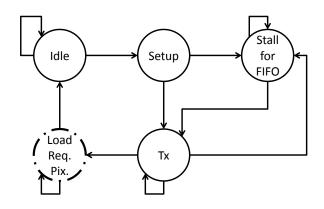

| D.1  | State diagram for the execution controller               | 162 |

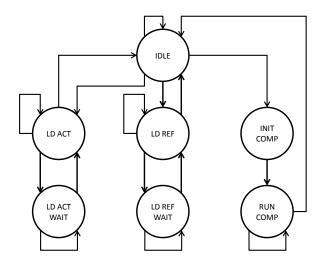

| D.2  | Dependency diagram for the top level controller          | 162 |

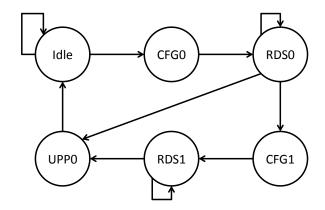

| D.3  | Flattened state diagram for request pixel FSMs           | 163 |

| D.4  | Hierarchical state diagram for request pixels FSM        | 164 |

| D.5  | Hierarchical state diagram for load requested pixels FSM | 164 |

# List of Tables

| $2.1 \\ 2.2$                                                   | A selection of video formats       19         Coding levels in H.265/HEVC       23                                                                                                                                                                                                                                  |

|----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $\begin{array}{c} 4.1 \\ 4.2 \\ 4.3 \\ 4.4 \\ 4.5 \end{array}$ | Bandwidth savings and costs from reference frame compression techniques35Motion estimation designs targeting GPU platforms37Comparisons between various systolic array (full search) implementations39ASICs and ASIPs targeting motion estimation41Throughput and efficiency comparison across the solution space45 |

| 5.1                                                            | The 32 instructions of the MEACC2 instruction set                                                                                                                                                                                                                                                                   |

| 5.2                                                            | Set burst REF X structure                                                                                                                                                                                                                                                                                           |

| 5.3                                                            | Set burst REF Y structure                                                                                                                                                                                                                                                                                           |

| 5.4                                                            | Set burst height structure                                                                                                                                                                                                                                                                                          |

| 5.5                                                            | Set burst width structure                                                                                                                                                                                                                                                                                           |

| 5.6                                                            | Set write pattern address structure                                                                                                                                                                                                                                                                                 |

| 5.7                                                            | Set PMV DX structure                                                                                                                                                                                                                                                                                                |

| 5.8                                                            | Set PMV DX structure                                                                                                                                                                                                                                                                                                |

| 5.9                                                            | Block ID mappings                                                                                                                                                                                                                                                                                                   |

| 5.10                                                           | Set BLKID structure                                                                                                                                                                                                                                                                                                 |

|                                                                | Set thresh top structure                                                                                                                                                                                                                                                                                            |

|                                                                | Set thresh bot structure                                                                                                                                                                                                                                                                                            |

|                                                                | Set ACT PT X structure                                                                                                                                                                                                                                                                                              |

| 5.14                                                           | Set ACT PT Y structure                                                                                                                                                                                                                                                                                              |

|                                                                | Set REF PT X structure                                                                                                                                                                                                                                                                                              |

|                                                                | Set REF PT Y structure                                                                                                                                                                                                                                                                                              |

|                                                                | Send pixels structure                                                                                                                                                                                                                                                                                               |

|                                                                | Write pattern DX structure                                                                                                                                                                                                                                                                                          |

|                                                                | Write pattern DY structure                                                                                                                                                                                                                                                                                          |

|                                                                | Write pattern JMP structure                                                                                                                                                                                                                                                                                         |

|                                                                | Write pattern VLD top structure                                                                                                                                                                                                                                                                                     |

|                                                                | Write pattern VLD bot structure                                                                                                                                                                                                                                                                                     |

| 5.23                                                           | Set output register structure                                                                                                                                                                                                                                                                                       |

|                                                                | Read REF MEM structure    61                                                                                                                                                                                                                                                                                        |

|                                                                | Read ACT MEM structure    61                                                                                                                                                                                                                                                                                        |

|                                                                | Read register operand lookup table                                                                                                                                                                                                                                                                                  |

| 5.27                                                           | Read register structure                                                                                                                                                                                                                                                                                             |

| 5.28 | Register read structure                                                    |

|------|----------------------------------------------------------------------------|

| 5.29 | Result read structure                                                      |

| 5.30 | Pixel request structure                                                    |

| 5.31 | Issue ping structure                                                       |

|      | Write burst ACT structure                                                  |

| 5.33 | Write burst REF structure                                                  |

| 5.34 | Start search structure                                                     |

| 5.35 | An example instruction stream                                              |

| 5.36 | Pattern ROM Contents in decimal                                            |

| 5.37 | Pattern ROM contents in binary                                             |

| 5.38 | Point reuse between stages in various search patterns                      |

| 6.1  | MEACC2 at a Glance                                                         |

| 7.1  | Setup transcript format                                                    |

| 7.2  | Pixel request transcript format                                            |

| 7.3  | Search result transcript format                                            |

| 7.4  | Points checked transcript format                                           |

| 8.1  | 16b FIFO throughput 102                                                    |

| 8.2  | Video format throughput requirements                                       |

| 8.3  | Compute efficiency of a 16xSAD 6 cycle pipeline, 2 cycle decision unit 104 |

| 8.4  | Pattern performance on BasketballDrill 832x480, 30 frames 105              |

| 8.5  | Pattern performance on BQMall 832x480, 30 frames 105                       |

| 8.6  | Pattern performance on Flowervase 832x480, 30 frames                       |

| 8.7  | Pattern performance on FourPeople 1280x720, 60 frames                      |

| 8.8  | Pattern performance on Johnny 1280x720, 60 frames                          |

| 8.9  | Pattern performance on Kristen and Sara 1280x720, 60 frames 106            |

| 8.10 | Hybrid search performance from simulation                                  |

| 8.11 | Hybrid search performance with tiling scalability 109                      |

## Chapter 1

## Introduction

The smartphone revolution is in full swing. Apple introduced the iPhone eight years ago, June 29th, 2007. Since then, Google has introduced the Android platform, and in 2013 an estimated 1 billion smartphones had been shipped worldwide. Each of these smartphones offers video capture and playback functionality. This rapidly growing market is driving even greater interest in fast video encode and decode functionality, while placing greater constraints on power budgets as even more functionality and sensors are brought onto the device. Additionally, the video being served onto smart devices is also available on PCs and new smart Televisions. At YouTube, a video streaming website, the number of videos served per day grew by 1 billion videos streamed between 2011 and 2012, to a total of 4 billion videos served per day.

A digital video stream consists of a series of still images, called frames which have a width and height, given in pixels. These frames are played back at a fixed rate, given in terms of frames per second (FPS). As the number of videos being served has grown, so has the size and quality of the video stream expected by customers. Television companies advertise the launch of their 4K products, which display frames as large as 7680 x 4320 pixels and YouTube supports 1080p videos delivered at 60 FPS.

Raw video streams tend to contain a large amount of redundant information, as each frame repeats every single pixel in the field of view even if nothing has changed. These raw video streams also require a tremendous amount of space, as each pixel requires at least several bytes of storage. Digital video compression reduces the size of the stored video file by eliminating redundant information while retaining enough of the original video stream so that it can be recreated on demand. The process is necessarily lossy, and designers trade off reconstructed video quality for storage space.

### 1.1 Project Goals

This work covers the design of a motion estimation hardware accelerator, named MEACC2, primarily for *inter*-frame motion estimation acceleration, with AsAP as a demonstration platform. As such the final device is expected to integrate cleanly with any compute platform which follows the general interconnect principles defined for AsAP2 and AsAP3. A key features of AsAP which makes it well suited as a test platform for video processing is the presence of fully-programmable independent processors and large on-chip shared memories. At the beginning the initial project requirements were defined as follows:

- Capable of real-time video processing in at least 1080p

- Compliant with the H.265 standard

- Capable of video processing in 4K formats

- Support for both built in and programmable search patterns

- Support for Full Search Pattern

- Explore the memory size vs. performance tradeoff in configurable accelerators

- Explore the use of Standard Cell Memories in AsAP based accelerator design

- Lay the groundwork for the development of an AsAP based H.265 Codec

### **1.2** Contributions

The time frame of this work extended further than initially expected, and so the main contributions include the following:

- The design and implementation of MEACC2, an H.265 capable hardware accelerator compatible with the 3rd generation AsAP interconnect, a circuit switched 16 bit dual-FIFO inter-block interface.

- Complete RTL, written in Verilog HDL

- Synthesized in 65 nm CMOS with a maximum frequency of 812 MHz post place and route

- The creation of matlab functional model of MEACC2, with the capability to generate test-benches for Post-Si validation.

- The introduction of a 12-point block-motion algorithm which fills the gap between high-cost/high-fidelity BMAs and low-cost/low-fidelity BMAs.

### 1.3 Overview

Chapter 2 introduces the fundamentals of digital video compression, including the motion estimation process. Chapter 3 covers the AsAP platform, features of interest, and how MEACC2 integrates with the whole system. Chapter 4 covers related work on motion estimation generally including other platforms such as FPGAs, ASICs, and CPU instruction set extensions. Chapter 5 introduces the MEACC2 architecture, including its instruction set, memory organization, and expected AsAP to MEACC2 interactions. Chapter 6 presents the MEACC2 datasheet, and post place and route die photo. Chapter 7 introduces the matlab model, its data structures, classes, and overall software architecture. Chapter 8 introduces the tradeoffs and performance estimations enabled by the matlab model. Chapter 9 summarizes this work's contribution, makes a few predictions, and outlines some ideas for future research and follow up.

## Chapter 2

## **Digital Video Compression**

The goal of digital video compression is to reduce the size of a video stream, by identifying redundant information, removing it, and replacing it with a scheme to recreate that information in the decompression step. There are two kinds of of redundancies: *inter*frame redundancy exists between frames in a video stream, *intra*-frame redundancy exists within a single frame of a video stream. Another way to think of these two kinds of redundancy is to think of *inter*-frame redundancy as describing a repetition of data over *time* while *intra*-frame redundancy is describing a repetition of data over *space*. An object which is present throughout an entire scene would be an example of the kind of redundancy that *inter*-frame compression seeks to remove. A large area sky taking up most of the tophalf of a scene would be the sort of information redundancy that *intra*-frame compression would remove.

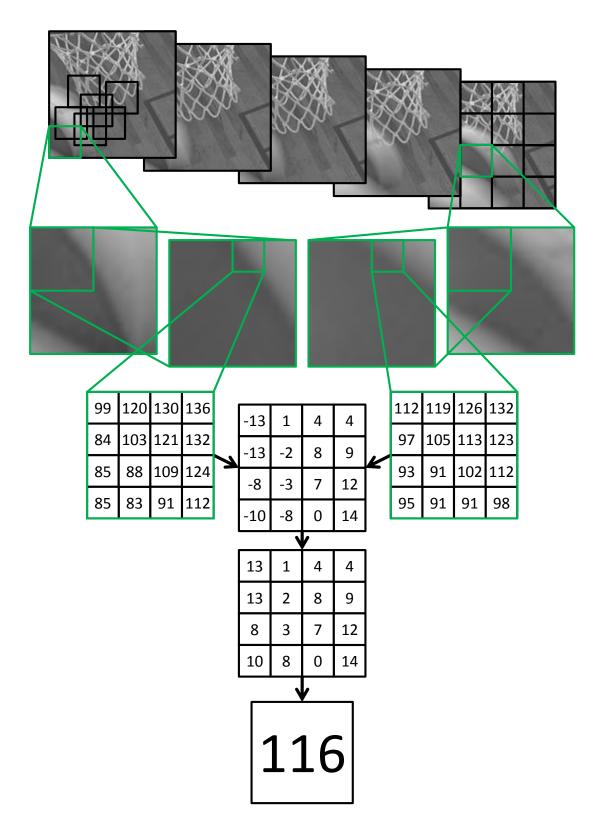

Redundancy is a qualitative description of an effect that humans see. The computer must be able to *quantify* the similarity between two sets of images. This quantification process generates a *figure of merit* which the compute process can use to determine whether or not the two images are redundant enough to remove without significant loss of image quality. Two examples of Figures of merit are mean absolute error (MAE) and sum of absolute difference (SAD) [1]. These Figures of merit are applied to pixel differences between the images. In the video coding standards that this work addresses (H.264 and H.265), the accepted Figure of merit is SAD. The advantages and disadvantages of particular Figures

Figure 2.1: Inter-frame redundancies exist between multiple frames of a video stream Figure 2.2: Intra-frame redundancies exist within a single frame of a video stream

of merit are beyond the scope of this work. Figure 2.3 gives a worked example of how to compute the SAD of two blocks of pixels.

For any two blocks of pixels in the pixel arrays A and R, of width N and height M the SAD is given:

$$SAD(A, R) = \sum_{i=0}^{N} \sum_{j=0}^{M} |A(x+i, y+j) - R(x+i, y+j)|$$

## 2.1 Video Coding Terms in Historical Context from H.261 to H.265

The standards can be viewed as a progression of terms and techniques. Video coding techniques have been largely accretive over the years, where each new standard adds additional coding tools to the standard and old coding tools continue to remain relevant. This has lead the computational complexity of video coding to scale not only along the axis of total number of pixel samples processed, but also along the axis of which coding features are supported by a particular encoder.

#### 2.1.1 H.261

Introduced the concept of the macroblock. Each macroblock is a 16x16 array of luma samples and two corresponding 8x8 arrays of chroma samples, using 4:2:0 sampling and a YCbCr color space [2]. The coding algorithm uses a hybrid of motion compensated interpicture prediction and spatial transform coding with scalar quantization, zig-zag scanning

Figure 2.3: Example SAD computation

and entropy encoding. The standard only defined the video decode process, the encoding was left open. This meant that encoders could pre-process data before encoding, and decoders could post-process after decoding - deblocking filters were a form a post-processing to reduce the appearance of block-shaped artifacts. It also only had support for integervalued motion vectors. Transform coding used an 8x8 Discrete Cosine Transform to reduce the spatial redundancy [2].

#### 2.1.1.1 Color Space

YCbCr describes the color space. YUV describes a file that uses YCbCr for color encoding. YCbCr breaks the color space into luma (Y, brightness) and chrominance (UV, color) components. Black and white only images have only luma components. Luminance is denoted Y and luma by Y. *Luminance* is perceptual brightness, what the eye/brain actually sees. *Luma* is electronic brightness eg. a voltage or a digital value.

#### 2.1.1.2 J:a:b Sampling

A quick way of describing the subsampling scheme for a region J pixels wide and 2 pixels high. The number of chrominance samples (Cr, Cb) in the first (even) row is denoted a, while the number of chrominance samples in the second (odd) row is denoted b [2]. Subsampling takes advantage of the fact that human vision cares more about brightness than color, and so coding techniques save bits by sampling the chrominance less carefully than the luminance.

#### 2.1.1.3 Entropy Encoding

Entropy encoding describes a wide range of lossless data compression schemes, which are data independent. Huffman and arithmetic coding are examples of entropy encodings. If the entropy characteristics of a data stream can be approximated beforehand, it can then be devolved into a static code, allowing data storage without any loss of fidelity [2].

#### 2.1.2 H.262

Introduced support for both interlaced and progressive video systems while dividing frames into 3 classes, I-frames (intra-coded), P-frames (predictive-coded), and B-frames (bidirectionally-predictive-coded). Allows for a number of subsampling schemes with 4:2:0 continuing to be the norm.

#### 2.1.2.1 Interlaced and Progressive Video

Interlaced video frames divide the image into two parts, a top-field and a bottomfield consisting of the odd numbered horizontal lines and even numbered horizontal lines respectively. Fields are transmitted and decoded in pairs. Progressive video means that fields and frames are the same, the image is not divided [2].

#### 2.1.2.2 Intra-Coded Frames (I-Frames)

An Intra-coded frame (I-Frame), is a compressed version of a raw frame that uses information from that frame only [2]. An I-frame then, can be decoded independently of its neighboring frames. Typically the I-frame is broken into 8x8 pixel blocks, the DCT is applied, the results quantized (this is where data fidelity is lost) and then compressed using run-length codes and other similar techniques.

#### 2.1.2.3 Predictive-Coded Frames (P-Frames)

P-frames can get a more compact compression than I-frames because they make use of data from previous I and P frames [2]. To generate a P-frame, the previous reference frame (either an I or P frame) is kept and the current frame is broken into 16x16 pixel macroblocks. Then, for each 16x16 macroblock in the current frame, the reference frame is searched for the smallest distortion match. The offset of the smallest distortion match is saved as a motion vector, and a residual between the two blocks computed. If not suitable match is found, the macroblock is treated like an I-frame macroblock.

#### 2.1.2.4 Bidirectionally-Predictive-Coded Frames (B-Frames)

B-frames are never reference frames and use information from both directions (from either I or P frames) [2]. They generally get an even more compact resulting compression than a P frame.

#### 2.1.2.5 Group of Pictures (GoP)

A series of I, B, and P frames. Useful for packing sets of frames together to be sent/handled as a group [2]. In H.262 usually every 15th frame is an I frame, but this is a flexible part of the standard. An example group of pictures might contain the following set of I, P, and B frames: IBBPBBPBBPBB.

#### 2.1.3 H.264

Further extended H.262 with new ways to do transforms, quantizations, and encodings, greater macroblock size coverage, and introduces new loss-resilience features.

#### 2.1.3.1 Variable Block-Size Motion Estimation (VBSME)

Macroblocks can take on a number of different sizes in VBSME schemes, instead of being fixed to 16x16. The valid sizes and shapes are:

- 16x16

- 16x8

- 8x16

- 8x8

- 8x4

- 4x8

- 4x4

These new shapes are used to get finer grain segmentation around moving regions in the video stream [2]. A macroblock can now be made up of multiple blocks (eg, 4 8x8 regions instead of 1 16x16 region) and each of those blocks can have their own motion vector. So each macroblock can have up to 32 motion vectors (a B macroblock with 16 4x4 partitions).

#### 2.1.3.2 Sub-Pixel Precision

Quarter-pixel precision is supported for greater accuracy. Chroma samples support  $\frac{1}{8}$  pixel precision since chroma is expected to be sampled at half the rate of luma in 4:2:0 mode.

## 2.1.3.3 Context-Adaptive Binary Arithmetic Coding and Variable-Length Coding (CABAC and CAVLC)

CAVLC and CABAC are used to code already quantized transform coefficient values [2]. There is a complexity tradeoff between CAVLC and CABAC, where CABAC can compress more efficiently than CAVLC, but is more computationally intensive [3]. CABAC was introduced in 2001 [4] and CAVLC in 2002 [5] and both were integrated into the H.264 standard recommendation [3].

#### 2.1.3.4 Exponential Golomb Coding (Exp-Golomb)

Exponential Golomb coding is another form of coding used for the more general forms of the standard (CABAC and CAVLC target primarily the image data, one would use Exp-Golomb for header tags and other metadata) [2].

#### 2.1.4 H.265

Up to double the compression effectiveness of HEVC (bitrate based) and the target is to allow up to 1000:1 compression for easily compressible video streams. Designed with the assumption of progressive video, so no explicit support for interlaced video [6].

#### 2.1.4.1 Coding Tree Units (CTUs) and Coding Tree Blocks (CTBs)

Coding tree units are analogous to the macroblocks of previous standards [7]. In 4:2:0 the CTU contains 3 CTBs, 1 luma CTB and 2 chroma CTBs. The size of the luma CTB is given  $L \times L$  where L = (16, 32, 64). The CTBs can be partitioned into smaller subunits called Coding Blocks (CBs), while the CTU is partitioned into Coding Units (CU) [7]. A CU typically contain the luma CB and the chroma CBs, for a total of 3 CBs. Each CU also has associated prediction units (PUs) and a tree of transform units (TUs). Prediction units have associated prediction blocks (PBs) ranging in size from 64x64 to 4x4. The transform units have associated transform blocks (TBs). There are transform functions defined for square TBs of 4, 8, 16, and 32 pixels.

Fundamentally, motion estimation hardware deals with the lowest level coding block. There are more possible block sizes, many used in asymmetrical motion prediction (AMP) [7].

#### 2.1.4.2 Allowed Prediction Block Sizes

- 64x64

- 32x64

- 64x32

- 32x32

- 16x32

- 32x16

- 16x16

- 8x16

- 16x8

- 8x8

11

• 4x8

• 8x4

#### 2.1.4.3 AMP Prediction Block Sizes

Support for asymmetrical motion prediction enables blocks oriented in both  $N \times (\frac{N}{4})$  and  $N \times (\frac{3N}{4})$  directions [7]. Reported experimental results demonstrate a 1% improvement in bit-rate at the cost of 15% additional encoding time [8]. The standard also establishes 4x8 and 8x4 as the minimum sizes for a prediction block (PB), and so AMP cannot be used for values of N smaller than 16.

- 16x64

- 48x64

- 64x16

- 64x48

- 8x32

- 24x32

- 32x8

- 32x24

- 4x16

- 12x16

- 16x4

- 16x12

#### 2.1.4.4 Motion Vector Signaling

Advanced motion vector prediction (AMVP) is used to pick probably candidates based on data from adjacent prediction blocks and the reference picture. There is also a merge mode that allows MVs to be inherited from temporal or spatially neighboring PBs. The prediction step helps guide the search, if using a pattern search, or pick a better search area candidate if using a full search [7].

#### 2.1.4.5 Motion Compensation

Quarter-sample precision is used for the MVs and 7 to 8 tap filters are used for interpolation of fractional-sample positions. H.264 used six-tap filtering with half-sample precision and linear interpolation to gain quarter-sample precision [2].

#### 2.1.4.6 Prediction Modes

Intrapicture prediction supports 33 directional modes, plus planar and DC modes (total of 35 modes).

#### 2.1.4.7 Context Adaptive Binary Arithmetic Coding (CABAC)

Similar to CABAC from H.264 but with several throughput-optimizations for parallel processing architectures and compression performance [7].

#### 2.2 H.264 and H.265 in Depth

IEEE promulgates a standard for video coding referred to as H.264 [3], and since 2011 has begun to promulgate a new standard, H.265 [9]. These standards allow the people who design hardware to encode video and the people who design hardware to decode video to be two separate subsets. There are additional standards which are also used for this purpose, Google, for instance, promulgates the V8 and V9 standards, which are roughly equivalent to H.264 and H.265. The primary goal of the H.265 coding standard was to increase the compression efficiency of video streams by 50% without negatively impacting the overall video quality [10]. Initial analysis of the H.265 standard indicates that the standard meets that goal, with demonstrations on multiple video streams [11]. Each of these standards contain a set of tools to use to compress a video stream. For H.265, the various effects of each of these tools has been broken out into different levels, trying to define a smooth tradeoff curve between computational complexity and final result quality [12].

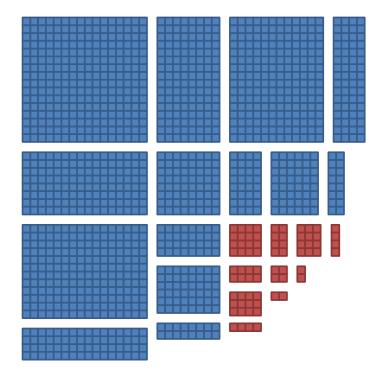

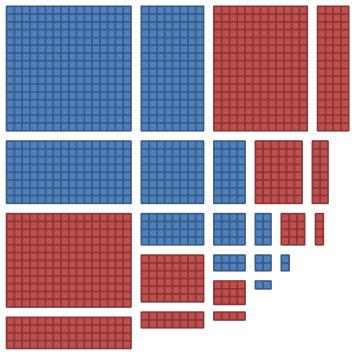

#### 2.2.1 Macroblocks and Coding Units

Motion estimation which makes use of variable block sizes is referred to Variable Block Size Motion Estimation (VBSME) [13]. H.264 made use of groups of pixels, called macroblocks to perform the encoding operation. Instead of matching pixels, the standard calls for blocks of pixels to be matched against other blocks of pixels. This technique was carried forward into the H.265 standard, in the form of coding units contained within a data-structure called a coding trees. For the purposes of this work, the important thing to know about both macroblocks and coding units, is that they can vary in size during operation. Different parts of a video stream can be coded with all the same size of block, or different sizes of blocks. Figure 2.4 gives a graphical representation of pixel block shapes supported in H.265 and H.264 compliant coding. There are a sit of shapes in H.265 referred to as the asymmetrical motion prediction vectors. These include all shapes that are not square or 1:2 ratio rectangular. Further investigation into AMP showed that there was only a 0.8% coding efficiency gain for a 14% increase in coding effort. Therefore, MEACC2 does not make use of AMP shapes. Figure 2.5 shows the AMP shapes which are not supported by MEACC2.

There were investigations into how to make the most effective macroblock divisions for a particular frame [14] and how to make those decisions quickly [15], targeting the H.264 application space. That research has been carried forward into coding trees.

#### 2.2.2 Coding Trees

As part of the shift to H.265, groups of pixels are grouped at multiple levels of hierarchy in a coding tree. A basic coding tree is very similar to the H.264 understanding of the frame, which contains many macroblocks of various sizes. In a coding tree, each frame has a coding tree, that coding tree has branches of various sizes, those branches have blocks of pixels of a size based on the depth of the branch node. Therefore, quick decisions on how to divide the coding tree result in faster compression speed, though an ideal coding tree would be necessary for maximum compression efficiency. An initial investigation into how to merge coding trees, also demonstrates that coding tree structures were 3% more effective

Figure 2.4: Shapes supported in H.265 and H.264. each square represents a 4x4 block of pixels. Blue shapes are only supported in H.265

Figure 2.5: Shapes supported in H.265 including AVMP. each square represents a 4x4 block of pixels. Red shapes are AMVP shapes and are not supported by MEACC2

than the equivalent direct mode in H.264 [16]. There has also been work done on how to predict the final shape of the coding tree, and using such prediction techniques combined with other hardware saving techniques have demonstrated a 2x performance increase and a 35% energy cost decrease [17].

#### 2.2.3 Slices and Tiles

Tiles are a technique available in H.265 to leverage parallel hardware [18]. These are similar to the slice technique used in H.264 [7]. Previous work with slices demonstrated that the overall coding process could be split into up to 16 slices with linear efficiency gains per slice added [19]. The expectation is that each tile is processed in parallel, and then information from each of the tile processing jobs can be used to refine the compression in future frames. In the meantime, from a hardware perspective, each tile can be treated as a separate, and independent unit, for much of the initial processing, including motion estimation. Our work then, can target a proof of concept of a single *tile* which can then be extrapolated outwards to video streams of significantly larger size. Tiles are not free, and does come with a cost in final video stream quality. The tile partition information is encoded in the final video stream, decoders then parse the tile information and use it to reassemble the stream at decode time.

#### 2.3 Block Motion Algorithms

Block motion algorithms (BMAs) encompass a class of search algorithms for finding the smallest SAD match for a set block of pixels. They are invariant with regards to the total size of the block of pixels, so the same algorithm can be applied to an 8x8 block of pixels and a 64x64 block of pixels. The design space of BMAs trades the total number of pixel blocks checked, for the *expected* fitness of the final block match.

#### 2.3.1 Full Search

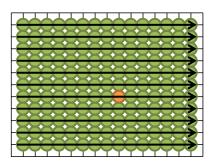

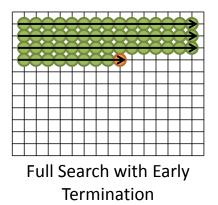

Full search is the simplest block motion algorithm, checking all possible blocks in a given search space. It guarantees the smallest distortion match within a search space is found, but it also costs the maximum amount of compute to find that match. It can be further enhanced with early termination logic so that the search is ended early if the smallest distortion match found so far is of a minimum threshold of quality, or with decimation, where the total number of points checked is reduced in an invariant manner (checking every other candidate in a full search would be a decimation by 2). Since it guarantees the highest quality match in a frame, the Full Search is a useful tool for determining the maximum quality of matches in a video stream, in order to quantify the quality degradation of search patterns which use less compute. Three worked examples of a full search implementation are given in Figure 2.6.

#### 2.3.2 Pattern Search

Pattern searches are also block motion algorithms, but they extend the full search by reducing the total number of block candidates checked, while still managing the reduction in match quality to an acceptable level. The acceptable level of degradation is dependent on the application space. These patterns can be thought of as an extension of the decimation technique used with full search algorithms. Instead of systematically checking every single possible candidate in a search range, a pattern search only checks a subset of those possible points. Some algorithm, which varies depending upon the pattern search, is used to determine which points to check, and in what order. Center-biased search patterns take as their starting point the position of the original block being compared. This follows from an observation, that if things in the video stream are static, the objects in that image do not move over time, and *spatially* local blocks would be good probable matches for the search between frames.

Once the initial point is checked, if the threshold value is not met additional points are checked. This is where the various center-biased search patterns begin to distinguish themselves from each other. The center not being a suitable match would imply that there has been some movement within the frame. A place to continue searching then, would be around the initial point. Checking all the points surrounding the center of the search would defeat part of the purpose of a search pattern (dramatically reducing the number of points checked), so the patterns are designed to capture as many possible motion directions,

**Full Search**

Full search patterns check every possible point in the search area in a fixed order. In this example, the all the green points are checked, and the orange point is found to have the best SAD.

Full Search with Decimation

In a decimated Full Search, not every single point is checked, but rather only a regular subset of the points. The search does however, still check every non-decimated point in the search area, so even though the orange point has the best SAD, the search continues.

In a Full Search with early termination, the search is ended when the first point which has a better SAD than a given threshold is found. This can be combined with decimation, but in this example it is not.

Figure 2.6: Different kinds of Full Search patterns

while still keeping the total of points checked to a minimum. A cross shaped search pattern would only capture motion in four directions, while a diamond shaped pattern can capture movement in up to eight directions. Each pattern is suitable for different kinds of motion. If a video stream's general motion behavior is known ahead of time, or that the class of video streams dealt with are known, it is possible to craft a more efficient search pattern that is application specific.

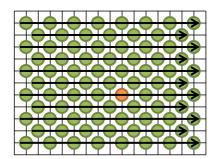

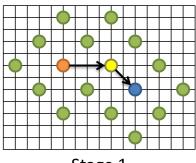

An example of a three stage, center-biased, diamond search pattern is given in Figure 2.7.

### 2.4 Video Formats

Each iteration of a codec, such as H.264 and H.265 give a series of levels which a video may be encoded in. These levels roughly represent the total bitrate that an encoder or decoder must be able to handle. However, these levels are not how consumers and designers actually interact with video. They interact with video formats, given in resolution and framerate. A number of commonly used video formats are given in Table 2.1, and the levels for H.265 are given, along with example formats and framerates in Table 2.2.

| General Use                    | Name             | Х    | Y    | Pixel Count per Frame |

|--------------------------------|------------------|------|------|-----------------------|

| Video Conferencing             | QCIF             | 176  | 144  | 25344                 |

| Video Comercineir              | CIF              | 352  | 288  | 101376                |

|                                | 480p             | 640  | 480  | 307200                |

|                                | 720p             | 1280 | 720  | 921600                |

| Digital Monitors / Televisions | 1080p            | 1920 | 1080 | 2073600               |

|                                | $2160\mathrm{p}$ | 3840 | 2160 | 8294400               |

|                                | 4320p            | 7680 | 4320 | 33177600              |

| Theater                        | Digital 4K       | 4096 | 2160 | 8847360               |

| Ineater                        | IMAX             | 5616 | 4096 | 23003136              |

Table 2.1: A selection of video formats

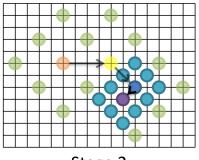

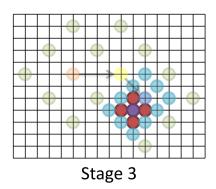

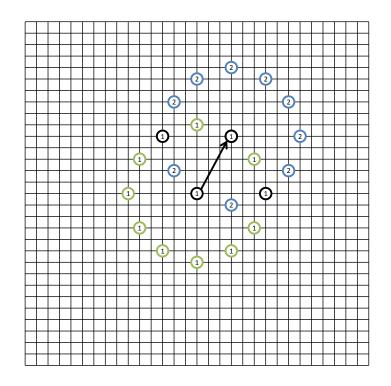

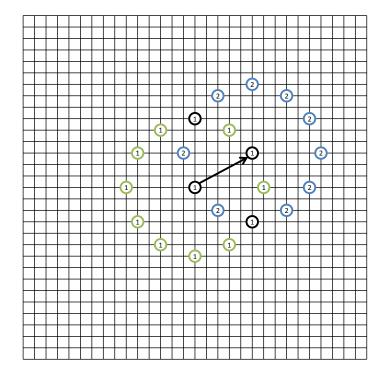

Stage 1

In stage 1, beginning from the search center (orange), 8 points in each direction are checked in a diamond pattern. As points with better SADs are found (yellow, then blue), the pattern moves and the diamond search is repeated. When no better point is found, the search changes to stage 2.

Stage 2

In stage 2, starting from the center found in stage 1, a more compact diamond pattern is used. Another candidate point with a better SAD is found (purple), and the pattern moves, as in stage 1. When no better point is found, the search changes to stage 3.

In stage 3, the final pattern used is a compact cross pattern of 4 points.

No better point is found, and as this is the final pattern of the search, the search terminates.

Figure 2.7: Example 3-stage pattern search

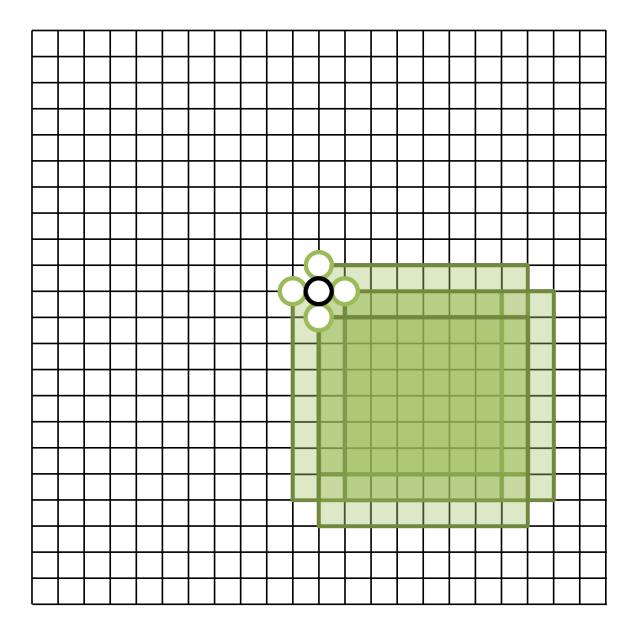

Figure 2.8: Relationship between search pattern points and pixel blocks

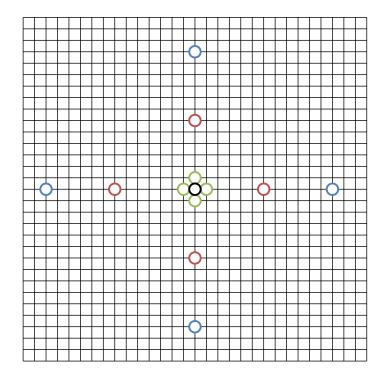

Figure 2.9: Cross patterns of varying width

Figure 2.10: Diamond patterns of varying width

| Level | Max Picture Size | Max Sample Rate | MaxSz FPS | Format | FPS    |

|-------|------------------|-----------------|-----------|--------|--------|

| 1     | 36864            | 552960          | 15.00     | QCIF   | 15.00  |

| 2     | 122880           | 3686400         | 30.00     | CIF    | 30.00  |

| 2.1   | 245760           | 7372800         | 30.00     | CIF    | 60.00  |

| 3     | 552960           | 16588800        | 30.00     | 480p   | 54.00  |

| 3.1   | 983040           | 33177600        | 33.75     | 720p   | 36.00  |

| 4     | 2228224          | 66846720        | 30.00     | 1080p  | 32.24  |

| 4.1   | 2220224          | 133693440       | 60.00     | 1080p  | 64.47  |

| 5     |                  | 267386880       | 30.00     | 2160p  | 32.24  |

| 5.1   | 8912896          | 534773760       | 60.00     | 2160p  | 64.47  |

| 5.2   |                  | 1069547520      | 120.00    | 2160p  | 128.95 |

| 6     |                  | 1069547520      | 30.00     | 4320p  | 32.24  |

| 6.1   | 35651584         | 2139095040      | 60.00     | 4320p  | 64.47  |

| 6.2   |                  | 4278190080      | 120.00    | 4320p  | 128.95 |

Table 2.2: Coding levels in H.265/HEVC

### 2.5 Decoders

Initial development on H.265 decoders is underway. Developers are beginning to grasp the overall differences between H.264 and H.265, and the important differences for those working with decoders were laid out as follows [20]:

- Macroblocks are replaced by Coding Units which support a maximum size of 64x64 pixels.

- Prediction Unit shapes may be asymmetrical

- Transform Units may be up to 32x32 pixels

- Up to 33 intra prediction modes

- Advanced skip modes and motion vector prediction

- New Adaptive Loop Filter (ALF)

- A Sample Adaptive Offset (SAO) is present after the deblocking filter

- Tools oriented for parallel processing

Work on high definition video decoders has continued as well, with decoders managing 4096x2160 at 60 FPS in 90 nm CMOS [21]. These decoders demonstrate that even with increasing encoder efficiency, the market and devices that would require that coding efficiency improvement exist and continue to develop.

## Chapter 3

## The AsAP Platform

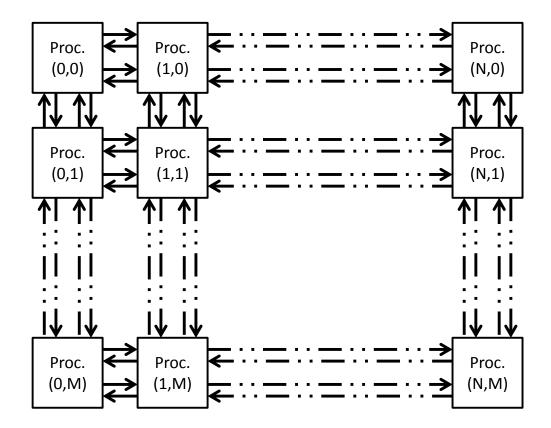

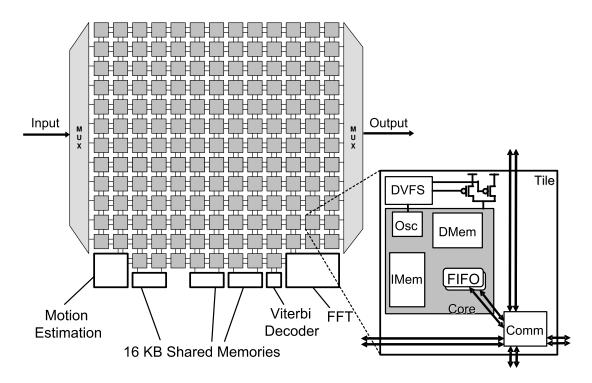

MEACC2 was developed to target the AsAP platform as its primary test platform, but AsAP as a platform encourages the development of loosely coupled, and therefore portable accelerator designs. AsAP is a fine-grain many-core architecture originally designed for DSP architectures, with a focus on scalability and power efficiency [22]. AsAP arrays consist of independently clocked processors communicating over dual-clock FIFOs, with each processor having its own instruction and data memories and executing a general instruction set [23], as shown in Figure 3.1. AsAP fabrics can be further enhanced with the addition of large memories or dedicated accelerators. These memory blocks and accelerators are connected to the array though those same dual-clock FIFOs, typically adjacent to two processors, as shown in Figure 3.2. The first generation of the AsAP platform contained 36 processors fabricated in 0.18  $\mu$ m<sup>2</sup>COMS [24], with a maximum operating frequency of over 600 MHz [25], and the second generation of the AsAP platform contained 167 full processor cores in 65 nm [26] with a maximum operating frequency of 1.2 GHz[27], and with enough compute to host a 1080p H.264 baseline residual encoder without any dedicated hardware [28].

### 3.1 Generalized Interface

The primary form of communication in the array is a 16b wide dual-clock domain FIFO [29]. The FIFOs between each node in the array allow for every processor and

Figure 3.1: An MxN AsAP array

Figure 3.2: A 167 core AsAP Array with big memories and accelerators

accelerator to be independently clocked. This also means that the accelerator design can target high frequency operation without worrying about the design of the rest of the array for high frequency operation as well. Additionally, the general interface of 16b words means that the accelerator can be easily modeled at a high level, as with the matlab model in Chapter 7.

# 3.2 Scalable Mesh

The scalability of the 2D mesh interconnect of an AsAP array means that as new technology nodes become available, the additional area can be put to productive use. The second generation AsAP array had a total of 167 processors, big memories, and three different kinds of hardware accelerators [30] including an FFT engine [31], and a previous generation motion estimation engine and the associated software encoder to take advantage of that accelerator [32]. With such scalability inherent to the platform, the priority is placed on developing accelerators which can also be scaled, as the latest iterations of the AsAP platform have a current maximum of 1000 processors in 32 nm [33]! Therefore, the MEACC2 was designed to make use of the Tiles paradigm introduced in H.265, which allows for the work of coding a video stream to be partitioned by subdividing the image and processing those sub-images in parallel [6]. Additionally, tools to map applications and the supporting software to take advantage of an accelerator to the device have already been developed and tested in other applications [34].

## 3.2.1 Circuit Switched Network

The AsAP platform also allows for connections beyond nearest neighbor using a low-cost circuit optimization for stable long-range links [35]. These long-range links, incorporated into a reconfigurable circuit-switched network [36], allow AsAP networks to host applications on fewer cores than an initial design would suggest [37]. Further research into the design of the packet routers used in the circuit switched network resulted in a bufferless router design with 60% greater throughput [38], and an advanced packet router with 7% savings in total energy expended per-packet [39]atran:vcl:phdthesis. These advances allow for AsAP based platforms to make heavy use of inter-processor communication links, suitable for streaming large amounts of data between nodes, such as found in video coding.