# **High Performance and Energy Efficient Multi-core Systems for DSP Applications**

By

ZHIYI YU

B.S. (Fudan University) June, 2000; M.S. (Fudan University) June, 2003

**DISSERTATION**

Submitted in partial satisfaction of the requirements for the degree of

DOCTOR OF PHILOSOPHY

in

Electrical and Computer Engineering

in the

OFFICE OF GRADUATE STUDIES

of the

UNIVERSITY OF CALIFORNIA

**DAVIS**

Approved:

Chair, Dr. Bevan M. Baas

Member, Dr. Vojin G. Oklobdzija

Member, Dr. Rajeevan Amirtharajah

Member, Dr. Soheil Ghiasi

Committee in charge 2007

© Copyright by Zhiyi Yu 2007 All Rights Reserved

## **Abstract**

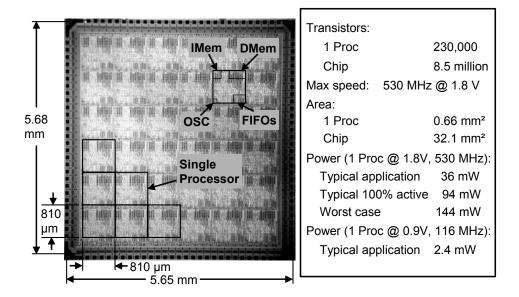

This dissertation investigates the architecture design, physical implementation, result evaluation, and feature analysis of a multi-core processor for DSP applications. The system is composed of a 2-D array of simple single-issue programmable processors interconnected by a reconfigurable mesh network, and processors operate completely asynchronously with respect to each other in a Globally Asynchronous Locally Synchronous fashion. The processor is called Asynchronous Array of simple Processors (AsAP). A  $6\times6$  array has been fabricated in a 0.18  $\mu$ m CMOS technology. The physical design concerns timing issues for robust implementations, and takes full advantages of their potential scalability. Each processor occupies  $0.66 \text{ mm}^2$ , is fully functional at a clock rate of 520–540 MHz under 1.8 V, and dissipates 94 mW while the clock is 100% active. Compared to the high performance TI C62x DSP processor, AsAP achieves performance 0.8–9.6 times greater, energy efficiency 10–75 times greater, with an area 7–19 times smaller. The system is also easily scalable, and is well-suited to future fabrication technologies.

An asymmetric interprocessor communication architecture is proposed. It assigns different buffer resources to the nearest neighbor interconnect and the long distance interconnect, can reduce the communication circuitry area by approximately 2 to 4 times compared to the traditional Network on Chip (NoC), with similar routing capability. A wide design exploration space is investigated, including supporting long distance communication in GALS systems, static/dynamic routing, varying numbers of ports (buffers) for the processing core, and varying numbers of links at each edge.

The use of GALS style typically introduces performance penalties due to additional communication latency between clock domains. GALS chip multiprocessors with large inter-processor FIFOs as AsAP can inherently hide much of the GALS performance penalty, and the penalty can even be driven to *zero*. Furthermore, adaptive clock and voltage scaling for each processor provides an approximately 40% power savings without any performance reduction.

## Acknowledgments

I would like to thank all of the individuals who made this work possible.

I want to thank professor Bevan Baas, for his academic guidance and financial support. His devotion and enthusiasm on research will effect me strongly in my future career. I want to thank my dissertation reading committee members including professor Vojin G. Oklobdzija, professor Rajeevan Amirtharajah, and professor Soheil Ghiasi, for their useful comments on my research. I want to thank previous VCL group members including Michael Lai, Omar Sattari, Ryan Apperson and Michael Meeuwsen. It was with them that I had a happy time when I first came to Davis, and their efforts and contributions helped to make the AsAP project successful, which becomes the strong basis of my dissertation. I want to thank current VCL group members including Eric Work, Tinoosh Mohsenin, Jeremy Webb, Wayne Cheng, Toney Jocobson, Zhibin Xiao, Paul Mejia, and Anh Tran; I always found I can learn something from them and they keep VCL group active.

I want to thank Intel Corporation, Intellasys Corporation, Xilinx, National Science Foundation (grant No. 0430090 and CAREER Award 0546907), UC MICRO, ST Microelectronics, SEM, SRC, and UC Davis Faculty Research Grant, for their generous financial donations to our research. I also want to thank Artisan, MOSIS, and TSMC; it was with their help that we had a successful fabrication of the AsAP chip.

I want to thank my family, my relatives and all of my friends. You might not know the details of my research area, but the support and help I get from you all might be more important than the pure academic help. It is because of you that I am a happy person and can keep pursuing my dreams.

# **Contents**

| Abstract |                 |               |                                                                 |      |  |  |

|----------|-----------------|---------------|-----------------------------------------------------------------|------|--|--|

| A        | cknov           | vledgme       | ents                                                            | iv   |  |  |

| Li       | List of Figures |               |                                                                 |      |  |  |

| Li       | st of T         | <b>Fables</b> |                                                                 | xi   |  |  |

| 1        | Intr            | oductio       | n                                                               | 1    |  |  |

|          | 1.1             | Challe        | nges                                                            | . 2  |  |  |

|          |                 | 1.1.1         | High performance and energy efficiency                          | . 2  |  |  |

|          |                 | 1.1.2         | Future fabrication technologies                                 | . 5  |  |  |

|          | 1.2             | Solutio       | on — multi-core systems                                         | . 6  |  |  |

|          | 1.3             | Contri        | butions                                                         | . 8  |  |  |

|          | 1.4             | Disser        | tation organization                                             | . 9  |  |  |

| 2        | Arcl            | hitectur      | re of the Multi-core System                                     | 11   |  |  |

|          | 2.1             | Key fe        | eatures of the multi-core processor                             | . 11 |  |  |

|          |                 | 2.1.1         | Chip multiprocessor and task level parallelism                  | . 12 |  |  |

|          |                 | 2.1.2         | Memory requirements of the targeted tasks                       | . 13 |  |  |

|          |                 | 2.1.3         | Simple single issue datapath                                    | . 14 |  |  |

|          |                 | 2.1.4         | GALS clocking style                                             | . 15 |  |  |

|          |                 | 2.1.5         | Wires and on chip communication                                 | . 17 |  |  |

|          | 2.2             | The As        | sAP processor system                                            | . 18 |  |  |

|          |                 | 2.2.1         | Single AsAP processor design                                    | . 19 |  |  |

|          |                 | 2.2.2         | Inter-processor communication — Reconfigurable 2-D mesh network | . 26 |  |  |

|          | 2.3             | Applic        | cation implementations and software                             | . 29 |  |  |

|          |                 | 2.3.1         | Application implementations                                     | . 29 |  |  |

|          |                 | 2.3.2         | Software                                                        | . 31 |  |  |

|          | 2.4             | Relate        | d work                                                          | . 32 |  |  |

|          |                 | 2.4.1         | Traditional DSP processors                                      | . 32 |  |  |

|          |                 | 2.4.2         | Pioneering multiprocessor systems and multi-core processors     |      |  |  |

|          |                 | 2.4.3         | Modern multi-core systems                                       | . 36 |  |  |

|          |                 | 2.4.4         | Distinguishing multi-core processors                            | . 40 |  |  |

|          | 2.5             | Summ          | arv                                                             | 11   |  |  |

| 3 | An l | Low-area Multi-link Interconnect Architecture                    | 45  |

|---|------|------------------------------------------------------------------|-----|

|   |      | 3.0.1 Background: traditional dynamic routing architecture       | 46  |

|   |      | 3.0.2 Background: static nearest neighbor interconnect           | 47  |

|   | 3.1  | Low-area interconnect architecture                               | 48  |

|   |      | 3.1.1 Asymmetric architecture                                    | 48  |

|   |      | 3.1.2 Theoretical analysis                                       | 50  |

|   |      | 3.1.3 Static routing vs. dynamic routing                         | 53  |

|   | 3.2  | Design space exploration                                         | 56  |

|   |      | 3.2.1 Single port vs. multiple ports for the processing core     | 56  |

|   |      | 3.2.2 Single link vs. multiple links                             | 59  |

|   | 3.3  | Supporting GALS long distance communication                      | 67  |

|   |      | 3.3.1 Source synchronization for long distance communication     | 69  |

|   |      | 3.3.2 Care more about the clock delay, less about skew or jitter | 70  |

|   | 3.4  | Implementation and results                                       | 70  |

|   |      | 3.4.1 Area                                                       | 71  |

|   |      | 3.4.2 Performance comparison                                     | 72  |

|   | 3.5  | Summary                                                          | 75  |

| 4 | Phys | sical Implementation of the GALS Multi-core Systems              | 77  |

|   | 4.1  | Timing issues of GALS multi-core systems                         | 77  |

|   |      | 4.1.1 Inter-processor timing issues                              | 78  |

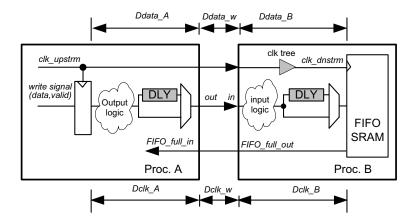

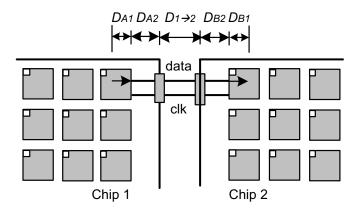

|   |      | 4.1.2 Inter-chip timing issues                                   | 81  |

|   | 4.2  | Scalability issues of GALS chip multiprocessors                  | 82  |

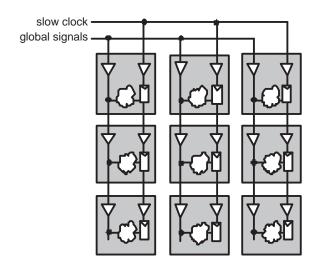

|   |      | 4.2.1 Clocking and buffering of global signals                   | 83  |

|   |      | 4.2.2 Power distribution                                         | 84  |

|   |      | 4.2.3 Position of IO pins                                        | 85  |

|   | 4.3  | A design example — implementation of AsAP                        | 85  |

|   |      | 4.3.1 Physical design flow                                       | 86  |

|   |      | 4.3.2 Implementation for high speed                              | 88  |

|   |      | 4.3.3 Testing                                                    | 89  |

|   | 4.4  | Summary                                                          | 90  |

| 5 | Resi | ults and Evaluation of the Multi-core System                     | 93  |

|   | 5.1  | Area, speed, and power                                           | 93  |

|   |      | 5.1.1 Small area and high area efficiency                        | 94  |

|   |      | 5.1.2 High speed                                                 | 96  |

|   |      | 5.1.3 High peak performance and low average power consumption    | 96  |

|   |      | 5.1.4 Result of communication circuitry                          | 98  |

|   | 5.2  | High performance and low power consumption for DSP applications  | 98  |

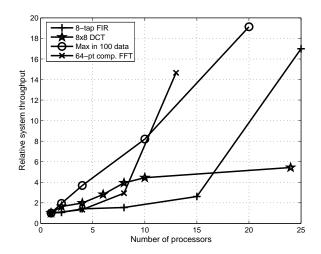

|   |      | 5.2.1 Performance scaling with the processor number              | 102 |

|   | 5.3  | Summary                                                          | 103 |

| 6 | Syst | tem Feature Analysis: GALS vs. Synchronous                       | 105 |

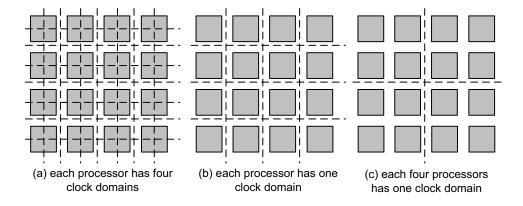

|   | 6.1  | Exploring the key GALS chip multiprocessor design options        | 106 |

|   |      | 6.1.1 Clock domain partition of GALS chip multiprocessors        | 106 |

|   |      | 6.1.2 Inter-processor network                                    | 107 |

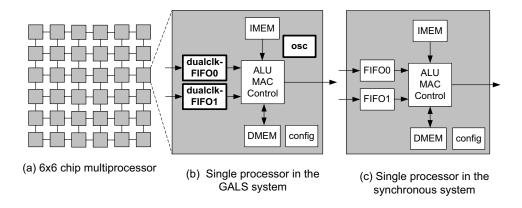

|   | 6.2  | Simulation platform — the GALS and non-GALS chip multiprocessors | 108 |

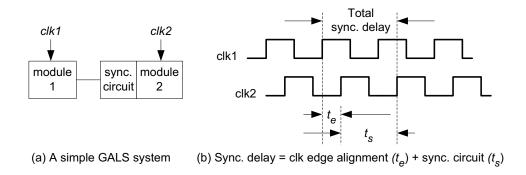

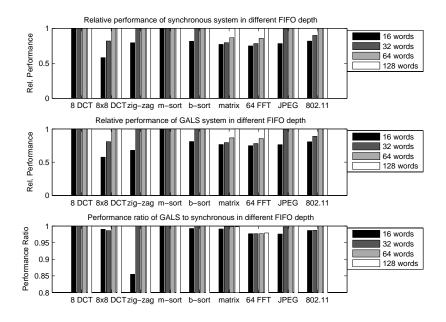

|   | 63   | Reducing and eliminating GALS performance penalties              | 109 |

|    |        | 6.3.1   | Related work                                                             | 109 |

|----|--------|---------|--------------------------------------------------------------------------|-----|

|    |        | 6.3.2   | Comparison of application performance: GALS versus synchronous           | 110 |

|    |        | 6.3.3   | Analysis of the performance effects of GALS                              | 111 |

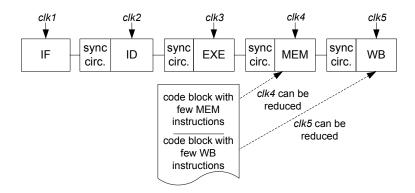

|    |        | 6.3.4   | Eliminating performance penalties                                        | 117 |

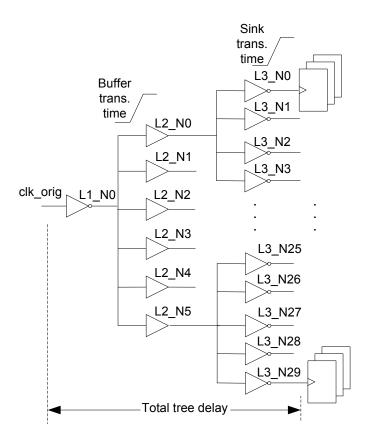

|    | 6.4    | Scalab  | ility analysis of GALS chip multiprocessors                              | 119 |

|    |        | 6.4.1   | Auto generated clock trees for different sizes of chip multiprocessors   | 119 |

|    |        | 6.4.2   | The effect of clock tree on system performance                           | 121 |

|    | 6.5    | Power   | analysis of adaptive clock frequency scaling                             | 123 |

|    |        | 6.5.1   | Related work—adaptive clock scaling of the GALS uniprocessor             | 124 |

|    |        | 6.5.2   | Unbalanced processor computation loads increases power savings potential | 125 |

|    |        | 6.5.3   | Finding the optimal clock frequency—computational load and position      | 126 |

|    |        | 6.5.4   | Power reduction of clock/voltage scaling                                 | 127 |

|    | 6.6    | Summ    | ary                                                                      | 128 |

| 7  | Con    | clusion |                                                                          | 131 |

|    | 7.1    | Future  | work                                                                     | 132 |

| G  | lossar | ·y      |                                                                          | 135 |

| Bi | bliog  | raphy   |                                                                          | 139 |

# **List of Figures**

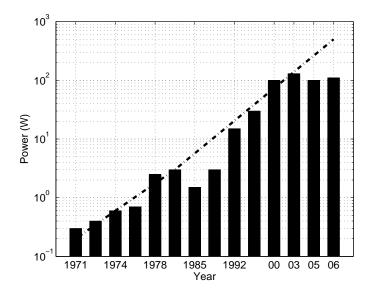

| 1.1  | Power consumption of Intel microprocessors from 1970 to 2006                          | 4  |

|------|---------------------------------------------------------------------------------------|----|

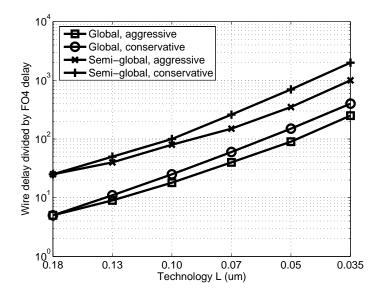

| 1.2  | Wire delays (in FO4s) for fixed-length (1 cm) wires                                   | 5  |

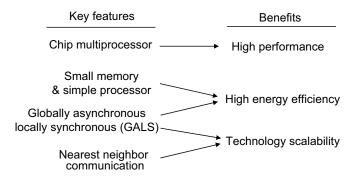

| 2.1  | Key features of AsAP and resulting benefits                                           | 12 |

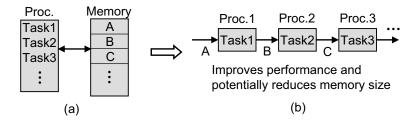

| 2.2  | Multi-task application executing models                                               | 12 |

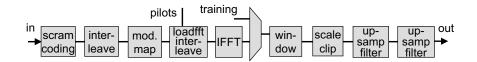

| 2.3  | IEEE 802.11a/g wireless LAN (54 Mbps, 5/2.4 GHz) baseband transmit path               | 13 |

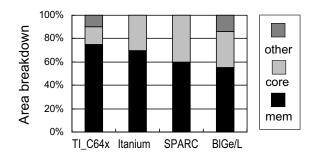

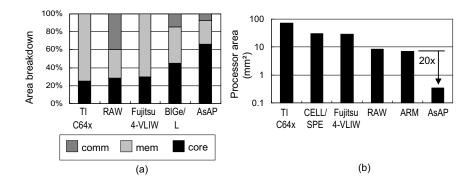

| 2.4  | Area breakdown of four modern processors; memory occupying most of the area .         | 13 |

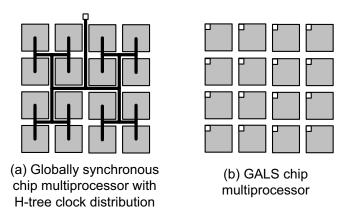

| 2.5  | Block diagrams of synchronous and GALS tile-based chip multiprocessors                | 16 |

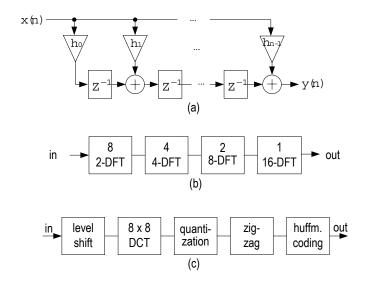

| 2.6  | Some <i>linear pipelined</i> algorithm models for DSP tasks and applications          | 18 |

| 2.7  | Block diagram of an AsAP processor                                                    | 19 |

| 2.8  | AsAP 9-stage pipeline                                                                 | 20 |

| 2.9  | Programmable clock oscillator                                                         | 21 |

| 2.10 | Physical distribution of oscillator frequencies across different processors           | 22 |

| 2.11 | Example waveform of clock halting and restarting                                      | 22 |

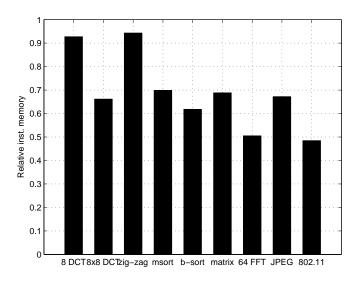

| 2.12 | Relative instruction memory cost by using <i>embedded NOP</i> instruction             | 24 |

| 2.13 | Comparison of three different addressing modes                                        | 26 |

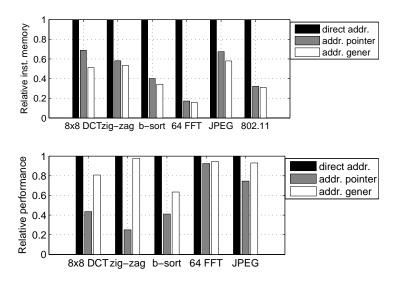

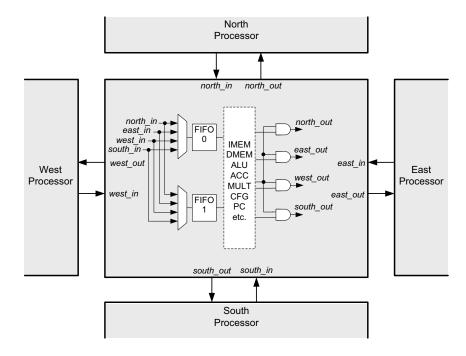

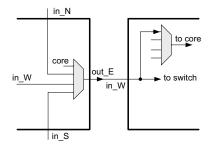

| 2.14 | Nearest neighbor inter-processor communication diagram                                | 27 |

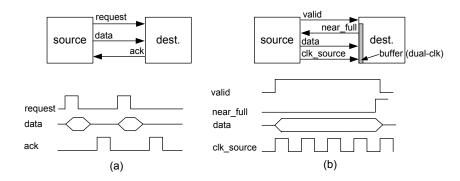

| 2.15 | Two strategies for communication in GALS systems                                      | 28 |

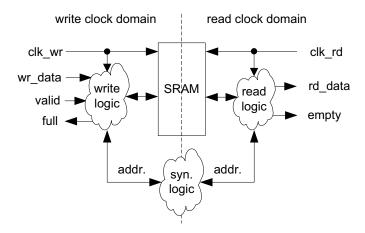

| 2.16 | Block diagram of the dual-clock FIFO                                                  | 28 |

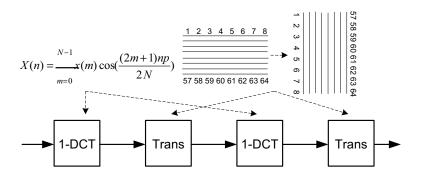

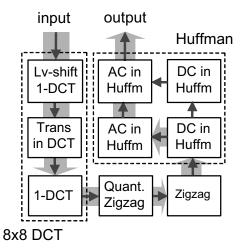

| 2.17 | 8 x 8 DCT implementation using 4 processors                                           | 30 |

| 2.18 | JPEG encoder core using 9 processors                                                  | 31 |

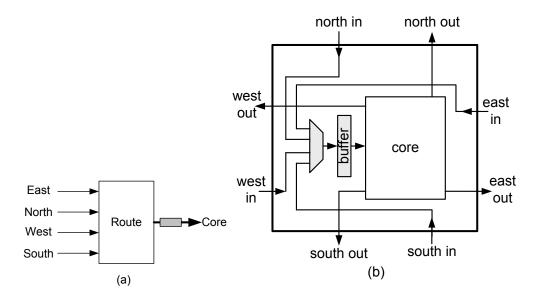

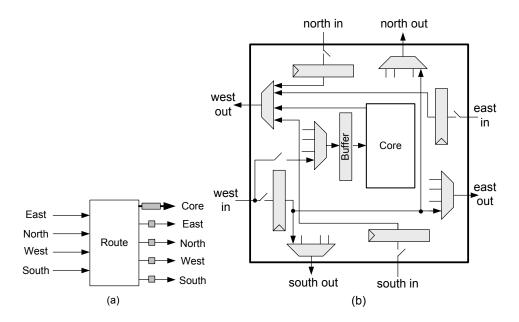

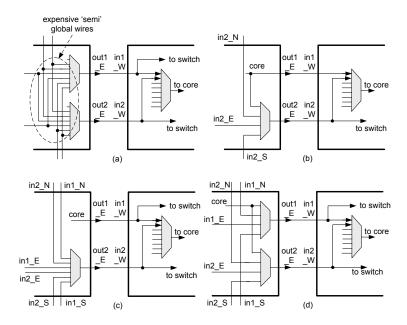

| 3.1  | Interprocessor communication in NoC systems and a generalized NoC architecture        | 46 |

| 3.2  | The concept and circuitry of the nearest neighbor interconnect architecture           | 47 |

| 3.3  | The concept and circuitry diagram of the proposed communication architecture          | 50 |

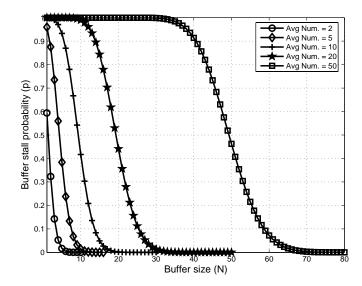

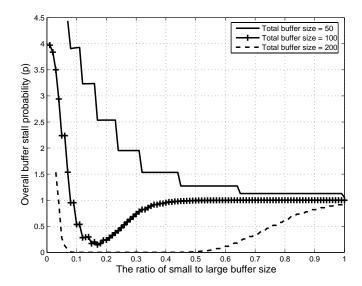

| 3.4  | Buffer stall probability $(p)$ along with buffer size $(N)$                           | 51 |

| 3.5  | The overall system buffer stall probability along the buffer size ratio               | 53 |

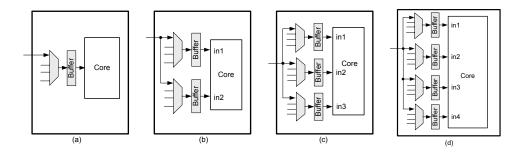

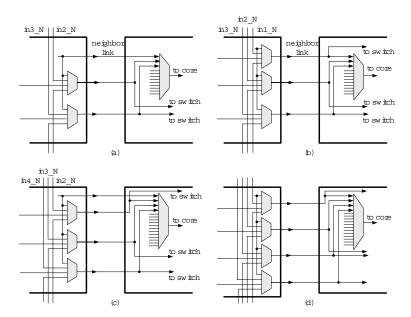

| 3.6  | Diagrams of architectures with various numbers of input ports for the processing core | 56 |

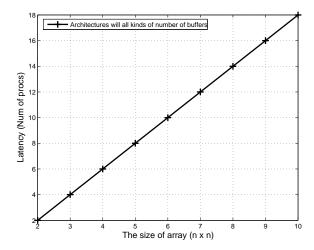

| 3.7  | The latency of architectures with different numbers of ports for one-to-one comm .    | 57 |

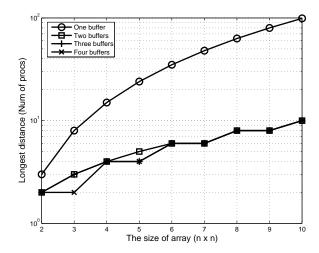

| 3.8  | The latency of architectures with different numbers of ports for all-to-one comm      | 58 |

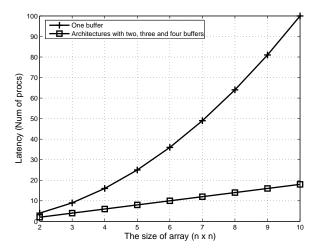

| 3.9  | The latency of architectures with different numbers of ports for all-to-all comm      | 59 |

| 3.10 | Diagram of inter-processor connection with one link at each edge                      | 60 |

| 3.11 | Inter-processor connections with double links                                         | 61 |

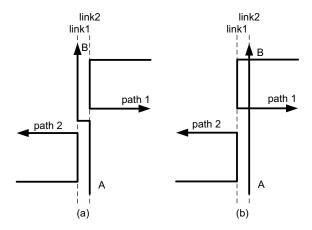

| 3.12 | Setup the interconnect path from point A to B                                         | 63 |

|      | Inter-processor interconnect with three and four links                                | 64 |

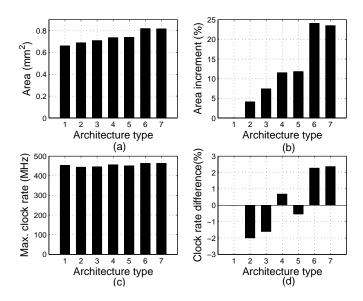

| 3.14 | layouts of seven processors with different communication circuitry                    | 65 |

| 3.15 | Comparing the processors with different communication circuitry                  | 66  |

|------|----------------------------------------------------------------------------------|-----|

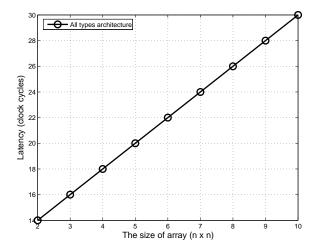

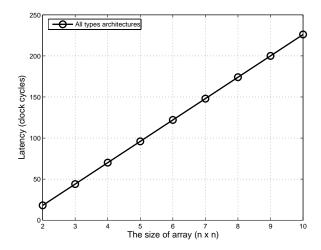

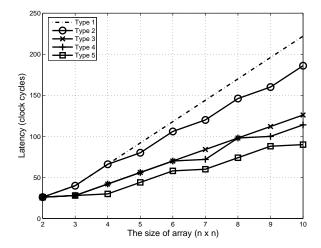

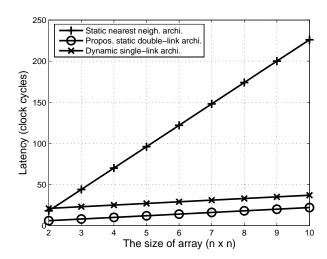

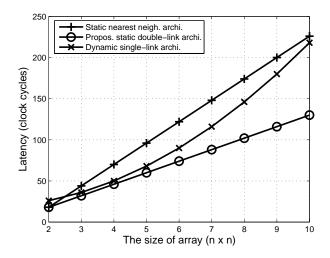

| 3.16 | The latency of interconnect architectures for one-to-one comm                    | 67  |

| 3.17 | The latency of interconnect architectures for all-to-all comm                    | 68  |

| 3.18 | The latency of interconnect architectures for all-to-one comm                    | 68  |

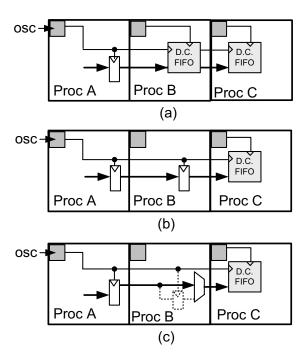

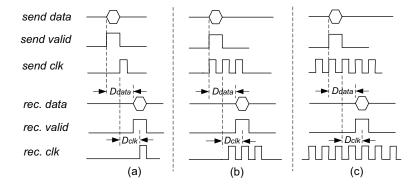

| 3.19 | Synchronization strategies for GALS long distance communication                  | 69  |

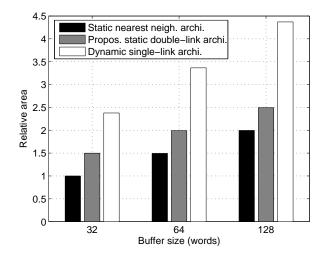

|      | The relative communication circuit area of several interconnection architectures | 71  |

| 3.21 | The latency of different interconnect architectures for one-to-one comm          | 72  |

| 3.22 | The latency of different interconnect architectures for all-to-one comm          | 73  |

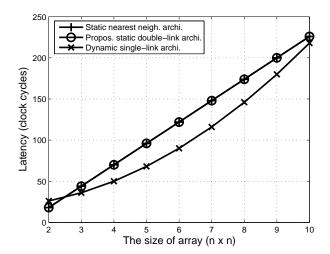

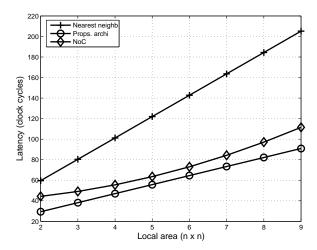

| 3.23 | Comparing the communication latency of three architectures                       | 73  |

|      | The latency of application models uniformly combined by the four basic patterns. | 74  |

|      |                                                                                  |     |

| 4.1  | An overview of timing issues in GALS chip multiprocessors                        | 78  |

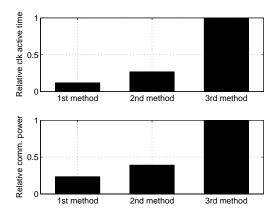

| 4.2  | Three methods for inter-processor communication                                  | 79  |

| 4.3  | Relative clock active time and communication power consumption                   | 79  |

| 4.4  | Circuit for the Fig. 4.2 (b) inter-processor communication method                | 80  |

| 4.5  | Configurable logic at the inter-processor boundary                               | 80  |

| 4.6  | Inter-chip communication                                                         | 82  |

| 4.7  | Global signals controlled by a low-speed clock                                   | 83  |

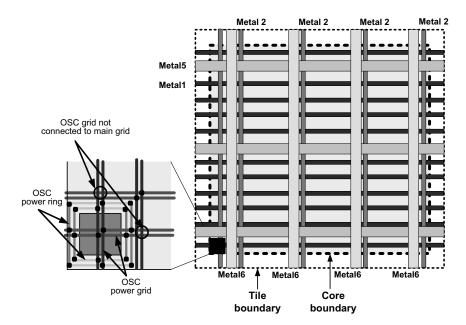

| 4.8  | An example power distribution scheme                                             | 84  |

| 4.9  | Pins connections between two processors vertically                               | 85  |

|      | Pins connections between two processors horizontally                             | 86  |

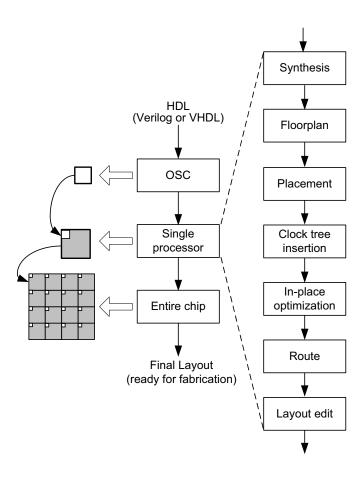

| 4.11 |                                                                                  | 87  |

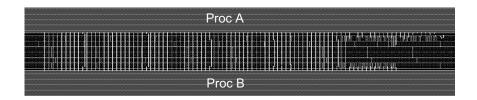

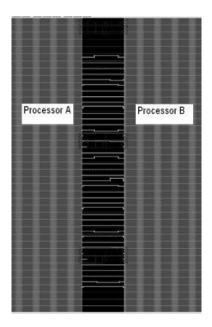

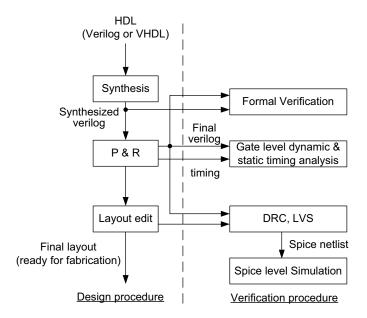

|      | Hierarchical physical design flow of a tile-based GALS chip multiprocessor       | 88  |

|      | A standard cell based back end design flow emphasizing the verification          | 89  |

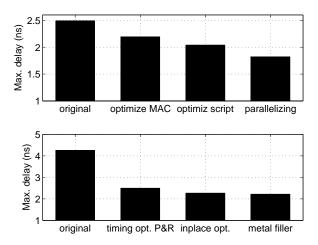

|      | Speed-up methods during synthesis and place and routing                          | 90  |

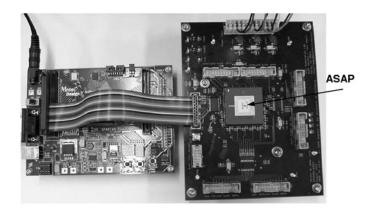

| 4.15 | AsAP board and supporting FPGA-based test board                                  | 91  |

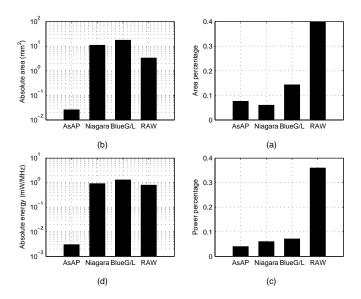

| 5.1  | Area evaluation of AsAP processor and several other processors                   | 94  |

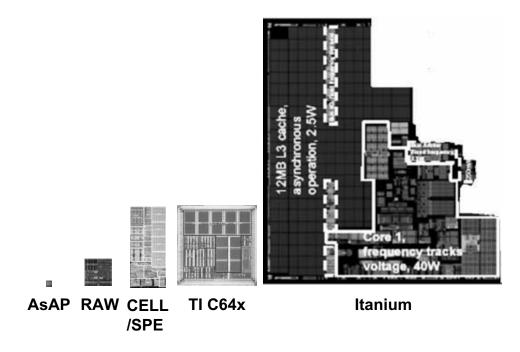

| 5.2  | Size of a single processing element in several chip multi-processor systems      | 95  |

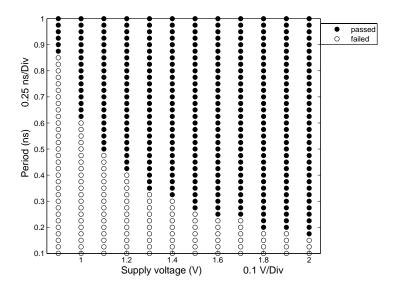

| 5.3  | Processor shmoo: voltage vs. speed                                               | 96  |

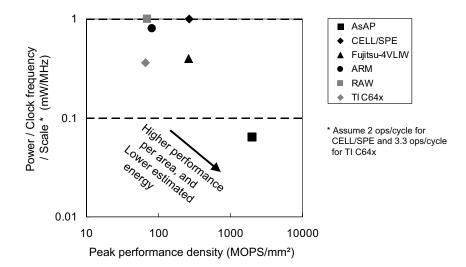

| 5.4  | Power and performance evaluation of AsAP processor and several other processors  | 97  |

| 5.5  | Comparison of communication circuit of four chip multiprocessors                 | 98  |

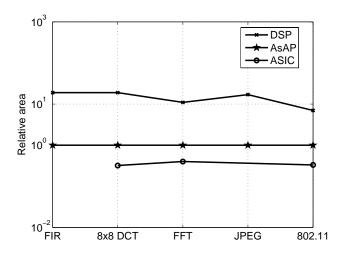

| 5.6  | Relative area for various implementations of several DSP kernels and apps        | 100 |

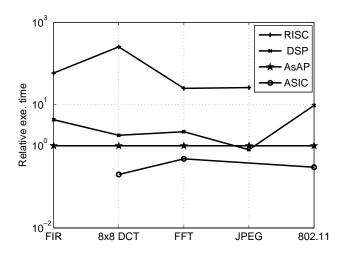

| 5.7  | Relative execution time for various implementations of several DSP apps          | 101 |

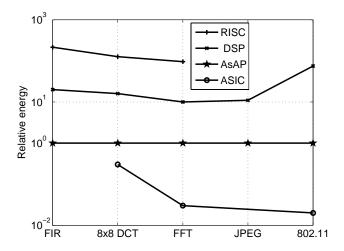

| 5.8  | Relative energy for various implementations of several DSP apps                  | 101 |

| 5.9  | Increase in system throughput with increasing number of processors               | 102 |

| 0.7  | increase in system amoughput with increasing number of processors                | 102 |

| 6.1  | Three example clock domain partitions                                            | 107 |

| 6.2  | Two chip multiprocessors                                                         | 108 |

| 6.3  | A GALS system boundary and timing of the synchronization delay                   | 109 |

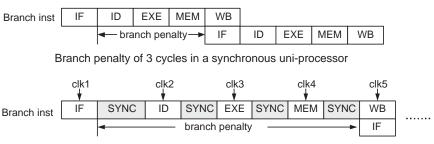

| 6.4  | Pipeline control hazard penalties                                                | 110 |

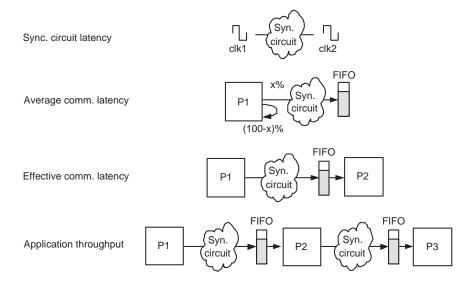

| 6.5  | Illustration of three key latencies and application throughput in GALS systesms  | 112 |

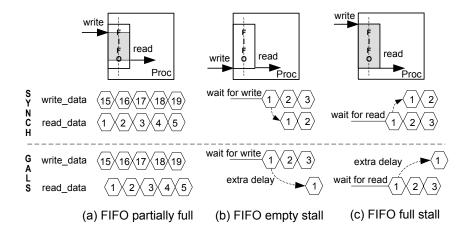

| 6.6  | FIFO operation during normal situation, and FIFO empty, and FIFO full            | 114 |

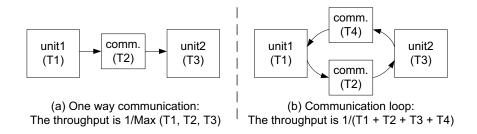

| 6.7  | System throughput in one way communication path, and communication loop path     | 115 |

| 6.8  | Data producer proc.1 and data consumer proc.2 both too slow                      | 116 |

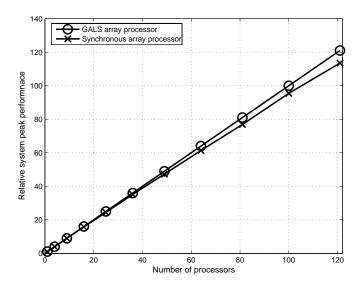

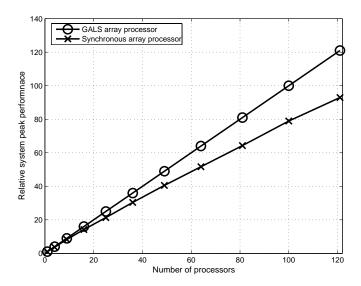

| 6.9  | Performance of synchronous and GALS array processors with different FIFO sizes   | 117 |

| 6.10 | Examples of multiple-loop links between two processors                           | 118 |

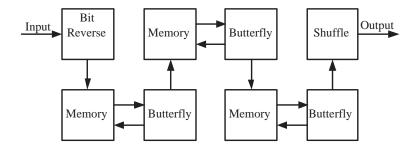

| 6 11 | 64-pt compelx FFT implementation                                                 | 119 |

| 6.12 | An example clock tree for a single processor                                 | 120 |

|------|------------------------------------------------------------------------------|-----|

| 6.13 | The peak performance of GALS and synchronous array processor                 | 122 |

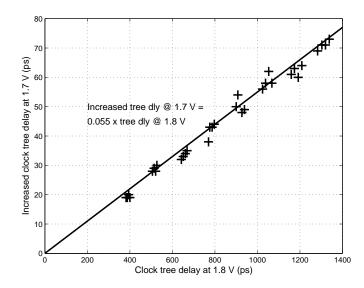

| 6.14 | Increased clock tree delay at 1.7 V supply voltage for different clock trees | 123 |

| 6.15 | The peak performanc with the number of processors                            | 124 |

| 6.16 | Clock scaling in a GALS uniprocessor                                         | 125 |

| 6.17 | Relative computational load of different processors in nine applications     | 126 |

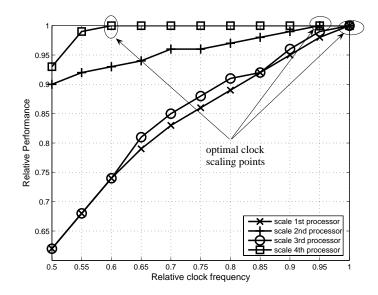

| 6.18 | Throughput changes with statically configured processor clocks               | 127 |

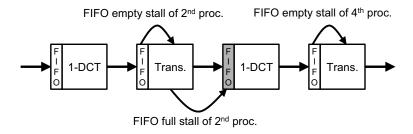

| 6.19 | Relationship of processors in the 4-processor 8×8 DCT application            | 127 |

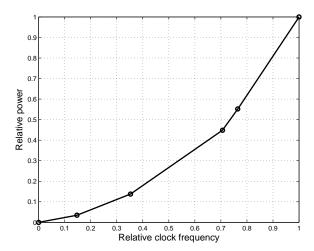

| 6.20 | The relationship between clock frequency and its power consumption           | 128 |

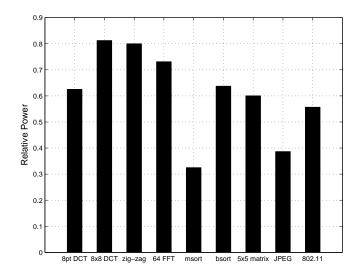

| 6.21 | Relative power of the GALS array processor                                   | 129 |

# **List of Tables**

| 1.1 | Example multi-core processors presented in ISSCC from 2003 to 2007                  | 7   |

|-----|-------------------------------------------------------------------------------------|-----|

| 2.1 | Memory requirements for common DSP tasks                                            | 14  |

| 2.2 | AsAP 32-bit instruction types and fields                                            | 23  |

| 2.3 | Classes of the 54 supported instructions                                            | 23  |

| 2.4 | Data fetch addressing modes                                                         | 25  |

| 2.5 | Computation load of the nine processors in JPEG encoder                             | 31  |

| 2.6 | Major features of some commercial DSP processors                                    | 33  |

| 2.7 | Comparison of the distinguished key features of selected parallel processors        | 41  |

| 2.8 | Comparison of the selected parallel processors                                      | 42  |

| 2.9 | Comparison of inter-element communication of selected parallel processors           | 43  |

| 3.1 | Data traffic of router's input ports and output ports for each processor            | 49  |

| 3.2 | The required buffer sizes for defined stall probabilities                           | 52  |

| 3.3 | Comparison of different interconnect approaches                                     | 55  |

| 3.4 | Interconnect architecture options for double links                                  | 62  |

| 4.1 | Typical timing constraint values for processor input and output delays              | 82  |

| 5.1 | Area breakdown in a single processor                                                | 94  |

| 5.2 | Estimates for a 13 mm $\times$ 13 mm AsAP array implemented in various technologies | 97  |

| 5.3 | Area, performance and power comparison of various processors for several apps       | 99  |

| 6.1 | Clock cycles (1/throughput) of several applications                                 | 111 |

| 6.2 | The fraction of the time the inter-processor communication is active                | 113 |

| 6.3 | Effective latency (clock cycles) of several applications                            | 115 |

| 6.4 | Data for globally synchronous clock trees for different array processors            | 121 |

## **Chapter 1**

## Introduction

Applications that require the computation of complex digital signal processing (DSP) workloads are becoming increasingly commonplace. These applications often comprise multiple DSP tasks and are frequently key components in many systems such as: wired and wireless communications, multimedia, large-scale multi-dimensional signal processing (e.g., medical imaging, synthetic aperture radar), some large-scale scientific computing, remote sensing and processing, and medical/biological processing. Many of these applications are embedded and are strongly energy-constrained (e.g., portable or remotely-located) and cost-constrained. In addition, many of them require very high throughputs, often dissipate a significant portion of the system power budget, and are therefore of considerable interest.

There are several design approaches for DSP applications such as ASICs, programmable DSPs and FPGAs. ASICs can provide very high performance and very high energy efficiency, but they have little programming flexibility. On the other hand, programmable DSPs are easy to program but their performance and energy efficiency is normally 10–100 times lower than ASIC implementations [1]. FPGAs fall somewhere in between. One-time fabrication costs for state of the art designs (e.g., 90 nm CMOS technology) are roughly one million dollars, and total design costs of modern chips can easily run into the tens of millions of dollars [2]. Programmable processors are the platforms be considered in this dissertation to allow high one-time fabrication costs and design costs to be shared among a variety of applications; but higher performance and energy efficiency are expected to be achieved using the architecture proposed in this dissertation compared to the

traditional programmable DSPs.

## 1.1 Challenges

Previous IC designers have been mainly concerned with fabrication cost and performance; minimizing the number of transistors to reduce the area is the main approach to reduce the cost; and increasing the clock frequency is the main approach to increase the performance. Currently, how to achieve energy efficiency and how to adapt to the advanced fabrication technologies become important challenges.

### 1.1.1 High performance and energy efficiency

## High performance innovations are challenging

Increasing the processor clock frequencies and using wide issue processor architectures have worked well to improve performance but recently have become significantly more challenging.

Deeper pipelining is one of the key techniques to increase the clock frequency and performance, but the benefit of the deeper pipeline is eventually diminished when the inserted Flip-Flop's delay is comparable to the combinational logic delay. Moreover, deeper pipeline stage increases cycles-per-instruction (CPI) and impacts negatively to the system performance. Researchers found that the depth per pipeline is approximately 8 Fanout-4 (FO4) inverter delays to obtain highest performance [3], which corresponds to 20–30 pipeline stages. The pipeline delay of some modern processor is already close to 10 FO4 [4] so that the deeper pipelining technique for high performance is reaching its limit. Also, increasing pipeline stages necessitates more registers and control logic, thereby further increasing design difficulty as well as power consumption. As reported by A. Hartstein [5], the optimum pipeline depth for maximum energy efficiency is about 22.5 FO4 delay (about 7 stage pipeline), using BIPS<sup>3</sup>/Watt as the metric—BIPS are billions of instructions per second.

The other key technology—shrinking the size of transistors to increase the clock frequency and integration capability—has amazingly followed Moore's Law [6] for about 40 years. Although the pace of this innovation is still going on, the limitations are right ahead in another couple of generations: either because of the physical limit when the size of transistors approaches the

1.1. CHALLENGES 3

size of atoms, or because of the fabrication cost prohibiting further progress.

Wide issue processor architectures such as VLIW and superscalar are another efficient approaches for high performance computation while their benefit is also quickly diminished when the issue width is more than 10; since most applications don't have so many independently parallel executable instructions in per fetch. For example, an 8-way VLIW TI high performance C6000 DSP [7] and an 8-wide superscalar RISC microprocessor [8] were reported in 2002, and there is no examples beyond this range till now.

#### Power dissipation becomes the key constraint

The high performance design of modern chips is also highly constrained by the power dissipation as well as the circuit constraints. Power consumption is generally dominated by dynamic power with the trend that leakage power is playing another key role. The dynamic power is formed by Equation 1.1

$$P = \alpha C V^2 f \tag{1.1}$$

where  $\alpha$  is the circuit state transition probability, C is the capacitance, V is the supply voltage, and f is the clock frequency. The leakage power mainly results from the reduction of the transistor threshold voltage [9] and is also highly dependent on the supply voltage. Most high performance technologies, such as increasing clock frequencies and increasing processor issues (which means increasing number of circuits and increasing capacitance) result in higher power consumption; all these imply a new era of high-performance design that must now focus on energy-efficient implementations [10].

Portable devices powered by battery certainly concern the power consumption since it determines their operational life time between each battery charging. Traditional non-portable systems such as PC also concern power consumption, since it highly determines the packaging costs, cooling system costs, and even limits the operation speeds and integration capacities of the systems. Figure 1.1 shows the power consumption of main Intel microprocessors from 1970 to 2006. The data between 1970 to 2000 is from S. Borkar [11] where he found that the changes of the power consumption follow the Moore's law increasing from 0.3 W to 100 W, and estimated that the processor power consumption will go up to 1000 W in a couple of years if this trend contin-

Figure 1.1: Power consumption of Intel microprocessors from 1970 to 2006; data between 1970 to 2000 are from [11]; data in 03, 05, 06 are from [12, 13, 14] respectively. Bars are the real values and the dashed line shows the trend

ues. Similarly to the power consumption, the power density increased significantly from a couple of Watts per mm<sup>2</sup> to about 100 Watts per mm<sup>2</sup> and becomes another key issue. This trend is halted in these years thanks to low power techniques such as voltage and frequency control technologies. The power consumption of recently reported microprocessors is still around 100 W. It also implies that 100 W is the power limit the current packaging technology and cooling technology can tolerate. Power consumption has become the highest constraint for designers and limits the achievable clock frequency and processor performance [10].

## The gap between dream and reality

H. D. Man shows a future ambient intelligent computing example which illustrates the gap between the future requirement and the current reality in both performance and power [15]. In his opinion, there will be three major devices in the future intelligent computing system. One is the main powerful computation components, like today's PC; its target performance is 1 TOPS, with power consumption less than 5 Watts, corresponding to the energy efficiency 100 to 200 GOPS/W. This requirement is about 1000 times higher than today's PC which has about 10 GOPS while consuming 100 W, corresponding to 0.1 GOPS/W. The second device is the handable devices powered by

1.1. CHALLENGES 5

Figure 1.2: Wire delays (in FO4s) for fixed-length (1 cm) wires [16]; global wires have larger width, height, and spacing which result in smaller resistance than semi-globle wires; aggressive and conservative are two extreme scaling projections to bound scaling parameters.

battery, like current mobile phone, targets to 10 to 100 GOPS with less than 1 W, corresponding to 10 to 100 GOPS/W. This requirement is about 10 times higher than current solutions which use RISC processors and/or DSP processors. The third component is the sensor network to receive and transfer information, powered by energy harvesting methods such as mechanical vibration, with power consumption less than 100 uW; developing such low power components is another challenging topic.

### 1.1.2 Future fabrication technologies

Future fabrication technologies are also imposing new challenges such as wiring and parameter variations.

In the early days of CMOS technology, wires could be treated as ideal. They transmit signals with infinite speed, without power consumption, and without coupling effect. This assumption is no longer true. For global wires, their length is nearly constant along with the technology scaling if the chip size stays the same; which makes their delay nearly constant. Compared to gate delay which scales down with the technology, the delay of the *global* and *long* wires scales up with the technology. As shown in Fig 1.2 [16], a 1 cm long global wire delay in modern 65 nm technology.

ogy is around 100 FO4 delay; which corresponds to more than one clock cycle period in modern processors and the global wires have to be pipelined or be eliminated through architecture level innovations. Similar with the delay, the power consumption of the long wires also scales up along with the technology compared to the gates. Besides the effect on delay and power consumption, the inductive and capacitive coupling between wires adds signal noise and impacts system reliability.

Furthermore, future fabrication technologies are expected to have tremendous variability compared to current technologies in both gates and wires. Fundamental issues of statistical fluctuations for submicron MOSFETs are not completely understood, but the variation increases leakage of transistor and causes a variation of the speed of individual transistors, which in turn leads to IC timing issues [17]. Borkar et al. reported chips fabricated in advanced nanometer technologies can easily have 30% variation in chip frequencies [18]. This variance will be present at time of fabrication and also have a time-varying component.

## 1.2 Solution — multi-core systems

In order to address the challenges in performance, power and future technologies, innovations on computer architecture and design are needed; and multi-core systems are one of the most, or the most promising technology. As was also pointed out by a computer architecture group at EECS department of UC Berkeley [19]: the "shift toward increasing parallelism is not a triumphant stride forward based on breakthroughs in novel software and architectures for parallelism; instead, this plunge into parallelism is actually a retreat from even greater challenges that thwart efficient silicon implementation of traditional uniprocessor architectures".

Deep submicron fabrication technologies enable very high levels of integration such as a recent dual-core chip with 1.7 billion transistors [13], thus reaching a key milestone in the level of circuit complexity possible on a single chip. A highly promising approach to efficiently use these circuit resources is the integration of multiple processors onto a single chip to achieve higher performance through parallel processing, which is called a multi-core system or a chip multiprocessor (CMP) system.

Multi-core systems can provide high energy efficiency since they can allow the clock frequency and supply voltage to be reduced together to dramatically reduce power dissipation during

Table 1.1: Major commercial general-purpose multi-core processors presented in ISSCC before 2007

| Year | Dual-core                   | Quad-core                | 8-core        |

|------|-----------------------------|--------------------------|---------------|

| 2003 | Mitsubishi's dual-core [20] |                          |               |

| 2004 | UltraSPARC [21]             |                          |               |

| 2005 | Itanium [13]                | Fujitsu's 4-core [22]    | CELL [23]     |

|      | SPARC [24]                  |                          |               |

|      | BlueGene/L [25]             |                          |               |

| 2006 | Xeon [14]                   |                          | Niagara1 [26] |

|      | x86 [27]                    |                          |               |

|      | Power $^{TM}$ [28]          |                          |               |

| 2007 | POWER6 [29]                 | Renesas' 4-core SoC [30] | Niagara2 [31] |

|      | Power $^{TM}$ [32]          | Opteron [33]             |               |

|      | Merom [34]                  |                          |               |

periods when full rate computation is not needed. Giving a simple example, assuming one uniprocessor is capable of computing one application with clock rate f and voltage v, and consuming power p; now if using a dual core system and assuming the application can be partitioned into two cores without any overhead, then each core only needs a clock rate f/2 and the voltage can be reduced accordingly; assuming a linear relation between voltage and clock frequency and the voltage is reduced to V/2, then the power dissipation of the dual core system will only be about p/4 calculated by Equation 1.1. Multi-core systems also potentially provide the opportunity to independently control each processor's clock and voltage to achieve higher energy efficiency, if different processors are in separate clock and voltage domains.

Furthermore, multi-core systems are suitable for future technologies. The distributed feature can potentially constrain the wires into one core and eliminate the global (long) wires. The multi-core systems also provide flexible approaches to treat each core differently by adjusting the mapped application, supply voltage, and clock rate; to utilize each core's specific features due to variations. For example, when one processor in the chip is much slower than the others, a low workload can be mapped on it without effecting system performance.

The multi-core systems have high scalability since a single processor can be designed and the system can be obtained by combining multiple processors. Thus the systems can be easily adjusted according to the required performance and cost constraints by changing the number of cores; which is much easier than changing the issue-width or the pipelining of uni-processors.

Table 1.1 shows the major commercial general-purpose multi-core processors presented in ISSCC before 2007. Multi-core processors started to emerge in 2003 and had a jump in 2005 and currently quad-core processors have become the main style. The trend to migrate from uniprocessors to multi-core processors is clear. The research community presented some more aggressive multi-core systems such as 16-core RAW [35] in 2003, 36-core AsAP [36] in 2006, and 80-core Intel chip [37] in 2007.

Although the trend is clear, there are a lot of issues that remain unclear to design an efficient multi-core processor. For example, what kind of processing element should be used in the multi-core systems; how to efficiently connect and communicate these multiple processing elements; and what is the clocking style to be used, etc. These are the questions this dissertation will try to investigate. Another big issue is related to the software such as how to describe applications and kernels to expose their parallel features; and how to program the multi-core processor using high level language; but those are beyond the main topic of this thesis.

## 1.3 Contributions

This dissertation makes a couple of contributions.

- It presents a successful multi-core processor, which is called Asynchronous Array of simple Processors (AsAP) [36, 38, 39], including its architecture design, physical implementation, application programming and results evaluation. The chip is organized by multiple simple single issue processors, interconnected by a reconfigurable mesh network, and operating in a globally asynchronous locally synchronous (GALS) [40] clock style. The system can efficiently compute many DSP applications, to achieve high performance, high energy efficiency, and is well suited for implementation in future fabrication technologies. The works not responsible by me are not included in this dissertation. Please refer to the publications of our group for the additional information, such as the details of the dual-clock FIFO design [41], the design of the large shared memory [42], the programming of an 802.11a/g wireless transmitter [43, 36], and the design of the MAC unit [44], etc.

- It generalizes the physical implementation techniques for multi-core processors with GALS

clock styles [45]. It presents the methodologies to handle the timing issues in GALS chip multi-processors including the inter-processor and inter-chip timing issues as well as the timing within a single processor. It takes full advantage of system scalability by taking care of the unavoidable global signals, the power distribution, and the processor IO pins.

- It investigates the performance, scalability, and power consumption effect when adopt GALS style to multi-core processors, by comparing to the corresponding totally synchronous systems [46]. It finds that this GALS array processor has a throughput penalty of less than 1% over a variety of DSP workloads, and this small penalty can be further avoided by large enough FIFOs and programming without multiple-loop communication links. It shows that unbalanced computational loads in chip multiprocessors increases the opportunity for independent clock frequency and voltage scaling to achieve significant power consumption savings.

- It proposes an asymmetric inter-processor communication architecture which uses more buffer resources for the nearest neighbor connections and fewer buffer resources for the long distance interconnect, and can save the area 2 to 4 times compared to the traditional NoC system while maintaining similar communication performance. It investigates the methodologies to support GALS clocking in long distance communication. It finds that using two or three links between each neighboring processors can achieve good area/performance trade offs for chip multiprocessors organized by simple single issue processors.

## 1.4 Dissertation organization

The organization of this dissertation is as follows. After the introduction, Chapter 2 introduces the architecture of the multi-core processor; Chapter 3 investigates the inter-processor communication system; Chapter 4 discusses and generalizes the physical design of tile-based GALS multi-core systems; Chapter 5 evaluates the measurement results of the fabricated multi-core chip; Chapter 6 analyzes the GALS effect on system features; and finally is the conclusion.

## **Chapter 2**

## **Architecture of the Multi-core System**

A multi-core processor system is proposed and designed, mainly for computationally-intensive DSP applications. The system comprises a 2-D array of simple programmable processors interconnected by a reconfigurable mesh network. Processors are each clocked by fully independent haltable oscillators in a GALS fashion.

The multi-core architecture efficiently makes use of task level parallelism in many complex DSP applications, and also efficiently computes many large DSP tasks through fine-grain parallelism to achieve high performance. The system uses processors with simple architecture and small memories to dramatically increase energy efficiency. The flexible programmable processor architecture broadens the target application domain and allows high one-time fabrication costs to be shared among a variety of applications. The GALS clocking style and the simple mesh interconnect greatly enhance scalability, and provide opportunities to mitigate effects of device variations, global wire limitations, and processor failures.

This chapter discusses the key features and architecture level design of the proposed multicore system which is called AsAP [36, 39] for an *Asynchronous Array of simple Processors*.

## 2.1 Key features of the multi-core processor

Several key features distinguish the AsAP processor. These features and the resulting benefits are illustrated in Fig. 2.1 and are discussed in greater detail in the following subsections.

Figure 2.1: Key features of AsAP and resulting benefits

Figure 2.2: Multi-task application executing on (a) a traditional architecture, and (b) a streamoriented multi-processor well suited for task level parallelism

### 2.1.1 Chip multiprocessor and task level parallelism

As discussed in Section 1.2, parallelization through multi-core systems are the future for high performance computation. Multi-core systems can use all types of parallelism techniques such as instruction-level parallelism, data-level parallelism and task-level parallelism.

Task-level parallelism can not be easily used on traditional sequentially-executing processors, but it is especially well suited for many DSP applications. As shown in Fig. 2.2 (a), the traditional system normally contains a powerful processor with a large memory, and executes the tasks of the application in sequence and stores temporary results into memory. The same application may be able to run on multiple processors using task level parallelism more efficiently as shown in Fig. 2.2 (b), where different processors handle different tasks of the application. Normally the data input of DSP applications is considered infinite length, so these processors can execute in parallel and achieve high performance. Also, the temporary results from each processor can be sent to the following processor directly and do not need to be stored in a large global memory, so less memory

Figure 2.3: IEEE 802.11a/g wireless LAN (54 Mbps, 5/2.4 GHz) baseband transmit path

Figure 2.4: Area breakdown of four modern processors; memory occupying most of the area

is necessary compared to the traditional method.

Task level parallelism is widely available in many DSP applications. Figure 2.3 shows an example of a modern complex application that exhibits abundant task-level parallelism—the transmit chain of an IEEE 802.11a/g wireless LAN transmitter. It contains more than 10 tasks, and each of them can be directly mapped to separate processors to take advantage of the available task level parallelism.

### 2.1.2 Memory requirements of the targeted tasks

With an ever increasing number of transistors possible per die, modern programmable processors typically use not only an increasing amount of on-chip memory, but also an increasing percentage of die area for memory. Figure 2.4 shows the area breakdown of four modern processors [7, 13, 24, 25] with memories that occupy 55% to 75% of the processor's area. Large memories reduce the area available for execution units, consume significant power, and require larger delays per memory transaction. Therefore, architectures that minimize the need for memory and keep data near or within processing elements can increase area efficiency, performance, and energy efficiency.

A notable characteristic of the targeted DSP and embedded tasks is that many have very

| · -                    |                             |                      |

|------------------------|-----------------------------|----------------------|

| Task                   | Instruction Mem requirement | Data Mem requirement |

|                        | (words)                     | (words)              |

| N-pt FIR               | 6                           | 2N                   |

| 8-pt DCT               | 40                          | 16                   |

| $8 \times 8$ 2-D DCT   | 154                         | 72                   |

| Conv. coding $(k = 7)$ | 29                          | 14                   |

| Huffman encoder        | 200                         | 350                  |

| N-point convolution    | 29                          | 2N                   |

| 64-point complex FFT   | 97                          | 192                  |

| Bubble sort            | 20                          | 1                    |

| N merge sort           | 50                          | N                    |

| Square root            | 62                          | 15                   |

| Exponential            | 108                         | 32                   |

Table 2.1: Memory requirements for common DSP tasks assuming a simple single-issue processor

limited memory requirements compared to general-purpose tasks. The level of required memory must be differentiated from the amount of memory that can be used or is typically used to calculate these kernels. For example, an N-tap filter may be programmed using a vast amount of memory though the base kernel requires only 2N data words. Table 2.1 lists the actual amounts of instruction and data memory required for several DSP tasks commonly found in DSP applications. These numbers assume a simple single-issue fixed-point processor. The data show that several hundred words of memory are enough for many DSP and embedded tasks—far smaller than the 10 KBytes to 10 MBytes per processing element typically found in modern DSP processors. Reducing memory sizes can result in significant area and power savings.

In addition to the inherent small memory requirement of DSP applications, some architectural features such as address generators and embedded NOP instructions can also contribute to reduce the instruction memory requirement, which will be discussed further in Section 2.2.1.

## 2.1.3 Simple single issue datapath

The datapath, or execution unit, plays a key role in processor computation, and also occupies a considerable amount of chip area. Uniprocessor systems are shifting from single issue architectures to wide issue architectures in which multiple execution units are available to enhance system performance. For chip multiprocessor systems, there remains a question about the trade-off between using many small single-issue processors, versus larger but fewer wide-issue processors.

Wide-issue processors work well when instructions fetched during the same cycle are highly independent and can take full advantage of functional unit parallelism, but this is not always the case. Furthermore, a large wide-issue processor has a centralized controller, contains more complex wiring and control logic, and its area and power consumption increases faster than linearly along with the number of execution units. One model of area and power for processors with different issues derived by J. Oliver et al. [47] shows that a single 32-issue processor occupies more than 2 times the area and dissipates approximately 3 times the power of 32 single-issue processors.

Using multiple single-issue processors, such as AsAP, can usually achieve higher area efficiency and energy efficiency, and they perform particularly well on many DSP applications since those applications are often made up of complex components exhibiting task level parallelism so that tasks are easily spread across multiple processors.

Using relatively simple (and hence small) processors in many-core chips also has some other advantages. For example, it is easier to apply dynamic clock and voltage scaling on smaller processors to achieve higher energy efficiency; it allows fitting more processors into a single chip and can introduce more redundant processors which can provide flexible fault tolerance computation techniques; and smaller processors are easier to design and verify, etc.

Some disadvantages of using large numbers of simple processors include extra interprocessor communication overhead when the applications have complex communication requirement, which is discussed further in Sec. 5.1.4; and the system is less efficient if the application is not possible to partition into independent tasks.

### 2.1.4 GALS clocking style

A globally synchronous clock style is normally used in modern integrated circuits. But with the larger relative wire delays and larger parameter variations of deep submicron technologies, it has become increasingly difficult to design both large chips, and chips with high clock rates. Additionally, high speed global clocks consume a significant portion of power budgets in modern processors. For example, 1/4 of the total power dissipation in the recent 2-core Itanium [13] is consumed by clock distribution circuits and the final clock buffers. Also, the synchronous style lacks the flexibility to independently control the clock frequency among system sub-components to

Figure 2.5: Block diagrams of (a) synchronous and (b) GALS tile-based chip multiprocessors; the small boxes in the right figure are the local oscillators for each processor

achieve increased energy efficiency. Furthermore, if using a synchronous clock style in multi-core systems, as shown in Fig. 2.5 (a), it has difficulty in taking full advantage of scalability benefits since the clock tree must be redesigned when the number of processors in the chip changes—which can result in a large effort in high performance systems. Also, clock skew in globally synchronous chips is expected to increase as the number of processors increases, which decreases performance.

The opposite clock style of globally synchronous—fully asynchronous in which there is no any timing reference exists—has the potential for speed and power improvements, but currently lacks EDA tool support, is difficult to design, and has large circuit overhead which reduces its efficiency.

The GALS [40] clocking style separates processing blocks such that each part is clocked by an independent clock domain. Its use enables the possibility of eliminating global clock distribution completely which brings power and design complexity benefits. Another significant benefit of GALS is the opportunity to easily and completely shut off a circuit block's clock (not just portions of the clock tree as with clock gating) when there is no work to do. Additionally, independent clock oscillators permit independent clock frequency scaling, which can dramatically reduce power dissipation in combination with supply voltage scaling [48]. Furthermore, when using the GALS clocking style in multi-core systems as shown in Fig. 2.5 (b), scalability is dramatically increased and the physical design flow is greatly simplified, since only a single processor must be designed and the entire chip can be generated easily by duplicating a single processor design.

### 2.1.5 Wires and on chip communication

As discussed in Section 1.1.2, wires are introducing greater delay, power consumption, and other impacts to chips, and the traditional communication methods within chips such as global bus has met considerable challenges. Global chip wires will dramatically limit performance in future fabrication technologies if not properly addressed since their delay is roughly constant with technology scaling—which leads to an increasing percentage of clock cycle time. A number of architectures such as systolic [49], RAW [35] and TRIPS [50] have specifically addressed this concern and have recommended using tile-based architectures. Therefore, architectures that enable the elimination of long high-speed wires will likely be easier to design and may operate at higher clock rates [16].

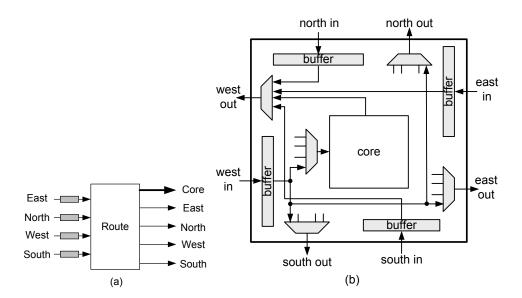

There are several methods to avoid global wires. Networks on chip (NoC) [51] treat different modules in a chip as different nodes in a network and use routing techniques to transfer data. Currently, most chip multiprocessors target broad general purpose applications and use complex inter-processor communication strategies. For example, RAW [35] uses a separate complete processor to provide powerful static routing and dynamic routing functions which is similar with NoC, BlueGene/L [25] uses a torus network and a collective network to handle inter-processor communication, and Niagara [26] uses a crossbar to connect 8 cores and memories. These methods provide flexible communication abilities, but consume a significant portion of the area and power in communication circuits.

Another method is local communication, where each processor communicates only to processors within a local domain. One of the simplest examples is nearest neighbor communication, where each processor directly connects and communicates only to immediately adjacent processors and the long distance communication is accomplished by software in intermediate processors. Most DSP applications, especially those that are stream-like [52], have specific regular features and make it possible to use a simple nearest neighbor communication scheme to achieve high area and energy efficiency, without a large performance loss. As can be seen from several popular industry-standard DSP benchmarks such as TI [53], BDTI [54], and EMBC [55], the most common tasks include FIR and IIR filtering, vector operations, the Fast Fourier Transform (FFT), and various control and data manipulation functions. These tasks can normally be *linearly pipelined*, as shown in Fig. 2.6 (a) and

Figure 2.6: Some *linear pipelined* algorithm models for DSP tasks and applications; (a) Transposed direct FIR filter, (b) 16-pt FFT, (c) JPEG encoder

(b), and the result from one stage can be pumped directly to the next stage without complex global communication. Complete applications containing multiple DSP tasks also have similar features, as examples shown in Fig. 2.6 (c) and Fig. 2.3 for the JPEG encoder and the 802.11a/g baseband transmitter. All these examples can be handled efficiently by nearest neighbor inter-processor communication.

The greatest challenge when using nearest-neighbor interconnects is efficiently mapping applications that exhibit significant long-distance communication. The communication architecture will be investigated further in Chapter 3, to achieve communication ability close to NoC with cost close to the nearest neighbor interconnect.

## 2.2 The AsAP processor system

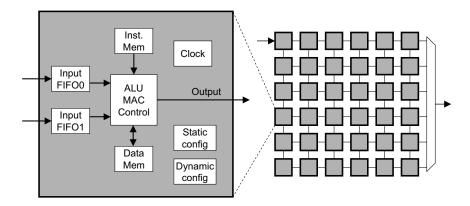

Figure 2.7 shows a block diagram of an AsAP processor and the fabricated processing array. Each processor is a simple single-issue processor, and contains: a local clock oscillator; two dual-clock FIFOs to provide communication with other processor cores; and a simple 16-bit CPU including ALU, MAC, and control logic. Each processor contains a 64-word 32-bit instruction memory and a 128-word 16-bit data memory. They also contain static and dynamic configuration logic to provide configurable functions such as addressing modes and interconnections with other

Figure 2.7: Block diagram of an AsAP processor

processors. Each processor can receive data from any two neighbors and can send data to any combination of its four neighbors. Each processor contains two input ports because it meshes well with the data flow graphs of the applications have studied. Clearly, two or more input ports are required to support graph fan-in and a third input port was found not frequently used. AsAP supports 54 RISC style instructions. It utilizes a memory-to-memory architecture with no register file. During the design phase, hardware was added only when it significantly increased performance and/or energy-efficiency for our benchmarks.

### 2.2.1 Single AsAP processor design

## Pipelining and datapath

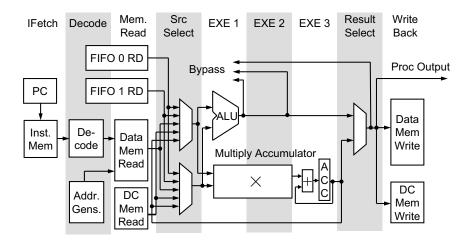

Each AsAP processor has a nine stage pipeline as shown in Fig. 2.8. The *IFetch* stage fetches instructions according to the program counter (PC). No branch prediction circuits are implemented. All control signals are generated in the *Decode* stage and pipelined appropriately. The *Mem Read* and *Src Select* stages fetch data from the data memory (Dmem), immediate field, the asynchronous FIFO interface from other processors, dynamic configuration memory (DCMem), the ACC accumulator register, or ALU/MAC forwarding logic. The execution stages occupy three cycles, and bypass logic is used for the ALU and MAC to alleviate data hazard pipeline penalties. The *Result Select* and *Write Back* stages select results from the ALU or MAC unit, and write the result to data memory, DC memory, or neighboring processors. To simplify pre-tapeout verification,

Figure 2.8: AsAP 9-stage pipeline

pipeline interlocks are not implemented in hardware, and all code is scheduled prior to execution by the programmer or compiler.

The MAC unit is divided into three stages to enable a high clock rate as well as the capability of issuing MAC and multiply instructions every cycle. The first stage generates the partial products of the 16×16 multiplier. The second stage uses carry-save adders to compress the partial products into a single 32-bit carry-save output. The final stage contains a 40-bit adder to add the results from the second stage to the 40-bit accumulator register (ACC). Because the ACC is normally read infrequently, only the least-significant 16 bits of the ACC are readable. More significant ACC bits are read by shifting those bits into the 16 LSBs. This simplification reduces hardware and relaxes timing in the final MAC unit stage which is the block's critical pipeline stage.

#### Local oscillator

Each processor has its own digitally programmable clock oscillator which provides the clock to each processor. There are no PLLs (phase lock loop), DLLs (delay lock loop), or global frequency or phase-related signals, and the system is fully GALS. While impressive low clock skew designs have been achieved at multi-GHz clock rates, the effort expended in clock tree management and layout is considerable [56]. Placing a clock oscillator inside each processor reduces the size of the clock tree circuit to a fraction of a mm<sup>2</sup>—the size of a processing element. Large systems can be

Figure 2.9: Programmable clock oscillator: an inverter ring with configurable tri-state inverters, ring size and frequency divider

made with arrays of processing elements with no change whatsoever to clock trees (that are wholly contained within processing elements), simplifying overall design complexity and scalability.

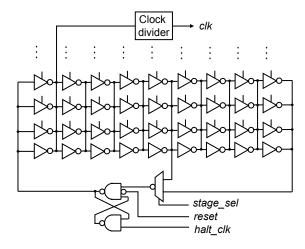

The oscillator is an enhanced ring oscillator as shown in Fig. 2.9. It is built entirely with standard cells and occupies only about 0.5% of the processor's area. Three methods are used to configure the frequency of the oscillator. First, the ring size can be configured to 5 or 9 stages using the configuration signal *stage\_sel*. Second, seven tri-state inverters are connected in parallel with each inverter. When a tri-state inverter is turned on, that stage's current drive increases, and the ring's frequency increases [57]. Third, a clock divider at the output divides the clock from 1 to 128 times. The *halt\_clk* signal and SR latch allow the oscillator to cleanly halt when the processor stalls without any partial clock pulses.

The oscillator has 2 ring-size-settings × 32768 tri-state-buffer-settings × 8 clock-divider-settings = 524,288 frequency settings, and measured results from the fabricated chip show that its frequency range is 1.66 MHz to 702 MHz over all possible configurations. In the range of 1.66 to 500 MHz, approximately 99% of the frequency gaps are smaller than 0.01 MHz, and the largest gap is 0.06 MHz. Despite the fact layout for all processors is exactly the same, variations largely due to the fabrication process cause different processors on the same die to perform differently than others. As Fig. 2.10 shows (data was measured by group member D. Truong), at the same configuration setting on the same chip the oscillator located in the bottom right processor has a frequency greater

| 506.7 | 498.5 | 497.4               | 505.9 | 510.1         | 520.9         |

|-------|-------|---------------------|-------|---------------|---------------|

| 507.6 | 506.2 | 498.9               | 506.8 | 510.6         | 520.8         |

| 508.4 | 507.2 | \$03.7 <sup>/</sup> | 507.3 | <b>5</b> 11.2 | 517.1         |

| 514.7 | 509.9 | 511.6               | 512.1 | 513.9         | 515.5         |

| 519.3 | 521.0 | 515.8               | 519.3 | 518.2         | 531.5         |

| 536.2 | 535.2 | 538.6               | 532.4 | 537.1         | <i>5</i> 41.2 |

Figure 2.10: Physical distribution of measured oscillator frequencies across different processors with the same configuration. Data are given in MHz with contour lines from 500 MHz to 540 MHz in 5 MHz steps.

Figure 2.11: Example waveform of clock halting and restarting

than 540 MHz, while several oscillators in the top row have frequencies less than 500 MHz, the frequency difference is about 10%.

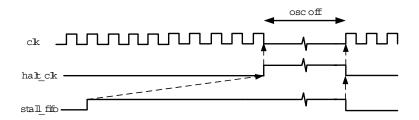

Processors stall when they try to read data from an empty FIFO or write data to a full FIFO. During these situations, the clock oscillator can be halted so that the processor consumes no power whatsoever except leakage. Figure 2.11 shows an example waveform for clock halting and restarting. Signal *stall\_fifo* is asserted when FIFO access is stalled due to either an empty input or full output condition. After a nine clock cycle period, during which the processor's pipeline is flushed, the signal *halt\_clk* goes high which halts the clock oscillator. The signal *stall\_fifo* returns low when the cause of the stall has been resolved; then *halt\_clk* restarts the oscillator in less than

Table 2.2: AsAP 32-bit instruction types and fields

| Instruction type | 6 bits | 8 bits | 8 bits | 8 bits | 2 bits |

|------------------|--------|--------|--------|--------|--------|

|                  | opcode |        |        | src2   | NOP    |

| Immediate        | opcode | dest   | imme   | ediate | NOP    |

| Branch           | opcode | _      | _      | target | NOP    |

Table 2.3: Classes of the 54 supported instructions

| Instruction class   | Number of instructions |

|---------------------|------------------------|

| Addition            | 7                      |

| Subtraction         | 7                      |

| Logic               | 11                     |

| Shift               | 4                      |

| Multiply            | 2                      |

| Multiply-accumulate | 6                      |

| Branch              | 13                     |

| Miscellaneous       | 4                      |

one clock period. Using this method, power is reduced by 53% and 65% for a JPEG encoder and a 802.11a/g transmitter application respectively.

#### **Instruction set**

AsAP supports 54 32-bit instructions with saturation modes, and supports three broad instruction formats. A summary of the 54 instructions is given in Tables 2.2 and 2.3. *General* instructions select two operands from memories, accumulator, FIFOs, and three ALU bypass routes; execute two operands by addition, subtraction, logic execution, multiply, or multiply-accumulate, and then select one destination from memories, accumulator and output ports. *Immediate* instructions receive input from a 16-bit immediate field. *Branch* instructions include a number of conditional and unconditional branch functions.

Seven addition instructions include: add and save low 16 bits; add and save high 16 bits; add with saturation; add with carry; add with carry and save high 16 bits; add with carry and with saturation; add by 1. Similar instructions exist for subtraction. The eleven logic instructions include: NOT, AND, NAND, OR, NOR, XOR, XNOR, MOVE, ANDWORD, ORWORD, and XORWORD. Besides the common conditional branch instructions which determine the destinations according to the conditional flags (such as negative, zero, carry and overflow), the instruction set also supports

Figure 2.12: Relative instruction memory cost by using embedded NOP instruction

branching when the FIFO is empty or full. The four miscellaneous instructions include a 16-bit bit-reverse instruction (for FFT addressing), an accumulator shift, a 16-bit move intermediate, and halt.

Two bits in each instruction define how many NOP operations (from 0 to 3) should follow after instruction processing, which allows inserting NOPs to avoid pipeline hazards without requiring additional NOP instructions and helps reduce instruction memory requirements dramatically. Figure 2.12 shows that instruction memory requirements can be reduced by approximately 30% for 9 applications. Below is one example to show how to use this instruction format where the data memory with address 1 is incremented by 1 and the result is sent to data memory address 2 and output port.

Add Dmem 2 Dmem 1 #1 NOP3

Add Obuf Dmem 2

Other than a bit-reverse instruction and a bit-reverse mode in the address generators which is useful for the calculation of the Fast Fourier Transform (FFT), no algorithm-specific instructions or hardware are used. While single-purpose hardware can greatly speed computation for specific algorithms, it can prove detrimental to the performance of a complex multi-algorithmic system and

| Addressing mode   | Example           | Meaning                                         |

|-------------------|-------------------|-------------------------------------------------|

| Direct            | Move Obuf Dmem 0  | Obuf ← Dmem[0]                                  |

| Address pointer   | Move Obuf aptr0   | $\texttt{Obuf} \leftarrow \texttt{Dmem[DCMem]}$ |

| Address generator | Move Obuf ag0     | $Obuf \leftarrow Dmem[generator]$               |

| Short immediate   | Add Obuf #3 #3    | Obuf ← 3+3                                      |

| Long immediate    | Move Obuf #256    | Obuf ← 256                                      |

| DCMem             | Move Obuf DCMem 0 | Obuf $\leftarrow$ DCMem[0]                      |

| Bypassing         | Move Obuf regbp1  | Obuf $\leftarrow$ first bypass                  |

| FIFOs             | Move Obuf Ibuf0   | Obuf $\leftarrow$ FIFO 0                        |

| ACC               | Move Obuf Acc     | Obuf ← ACC[15:0]                                |

Table 2.4: Data fetch addressing modes

limits performance for future presently-unknown algorithms—which is one of the key domains for programmable processors.

#### **Data addressing**

AsAP processors fetch data at pipeline stage *Mem Read*, using the addressing modes listed in Table 2.4. Three methods are supported to address data memory. *Direct* memory addressing uses immediate data as the address to access static memory locations; four *address pointers* access memory according to the value in special registers located in DCMem; and four *address generators* provide more flexible addressing such as automatic increment and decrement, with special-purpose hardware to accelerate many tasks. In addition to the data memory, AsAP processors can also fetch data from another 6 locations: 1) short immediate data (6 bits) can be used in dual-source instructions, 2) long immediate data (16 bits) can be used in the move immediate instruction, 3) the DCMem's configuration information, 4) three bypass paths from the ALU and MAC units to accelerate execution, 5) the two processor input FIFOs, and 6) the low 16 bits of the accumulator register.

Address generators help reduce the required instruction memory for applications since they can handle many complex addressing functions without any additional instructions. The upper figure of Fig. 2.13 shows the estimated relative instruction cost for a system using three addressing modes to fulfill the same functions. Compared to systems primarily using direct memory addressing and address pointers, the system containing address generators reduces the number of required instructions by 60% and 13% respectively. Also, using address generators can increase system

Figure 2.13: Comparison of relative instruction memory cost and system performance for three different addressing modes. Comparisons are made against the *direct address* case which uses straight line code with pre-calculated addresses only.

performance. As shown in the lower figure of Fig. 2.13, it comes within 85% of the performance of a system using direct addressing with pre-calculated addresses, and approximately 2 times higher performance compared to a system using address pointers alone.

#### 2.2.2 Inter-processor communication — Reconfigurable 2-D mesh network

The AsAP architecture connects processors via a configurable 2-dimensional mesh as shown in Fig. 2.14. To maintain link communication at full clock rates, inter-processor connections are made to nearest-neighbor processors only. Each processor has two asynchronous input data ports and can connect each port to any of its four nearest neighboring processors. The input connections of each processor are normally defined during the configuration sequence after powerup. The output port connections can be changed among any combination of the four neighboring processors at any time through software. Input ports are read and output ports written through reserved program variables and inter-processor timing is in fact invisible to programs without explicit software synchronization.

A number of architectures including wavefront [49], RAW [35], and TRIPS [50], have specifically addressed this concern and have demonstrated the advantages of a tile-based architec-

Figure 2.14: Nearest neighbor inter-processor communication diagram

ture. AsAP's nearest neighbor connections result in no high-speed wires with a length greater than the linear dimension of a processing element. The inter-processor delay decreases with advancing fabrication technologies and allows clock rates to easily scale upward. Longer distance data transfers in AsAP are handled by routing through intermediary processors or by "folding" the application's data flow graph such that communicating processing elements are placed adjacent or near each other.

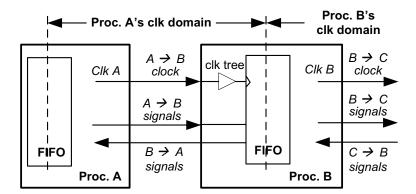

#### Source synchronization for GALS systems

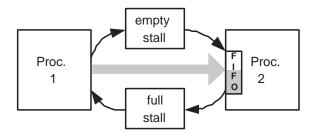

GALS systems introduce modules with different clock domains and the communication between those modules requires special concerns. The methods can be classified into two categories. The first method is asynchronous handshake [58] as shown in Fig. 2.15 (a). The source sends a *request* signal and one single data at each transaction and can start a new data transfer till it receives the *acknowledge* signal from the destination. A corresponding latency exists for each data transfer in this method. In order to sustain higher throughput, coarse grain flow control or *source synchronous* method can be used as shown in Fig. 2.15 (b), where the clock of the source processor

Figure 2.15: Two strategies for communication in GALS systems. (a) asynchronous handshake which requires more than one clock cycle for each transaction, and (b) source synchronous flow control which can sustain one transaction per clock cycle.

Figure 2.16: Block diagram of the dual-clock FIFO used for asynchronous boundary communication